基于FPGA的高速實時數(shù)據(jù)采集系統(tǒng)設計

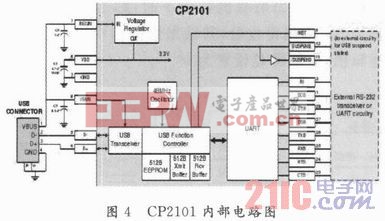

CP2101是一種高度集成的USB轉UART橋接器,提供一個使用最小化的元件和PCB空間實現(xiàn)RS 232轉USB的簡便的解決方案。該芯片包含一個USB 2.0全速功能控制器、USB收發(fā)器、振蕩器和帶有全部的調制解調器控制信號的異步串行數(shù)據(jù)總線(UART),全部功能集成在一個5 mm×5 mm MLP-28封裝的IC中。無需其他的外部USB元件。主要引腳有:

VDD:2.7~3.6 V電源電壓輸入或者3.3 V電壓調節(jié)器輸出;

:器件復位。內部端口或VDD監(jiān)視器的漏極開路輸出。一個外部源可以通過將該引腳驅動為低電平至少15 s來啟動一次系統(tǒng)復位;

REGIN:5 V調節(jié)器輸入。此引腳為片內電壓調節(jié)器的輸入;

VBUS:VBUS感知輸入。該引腳應連接至一個USB網絡的VBUS信號,當連通到一個USB網絡時,該引腳上的信號為5 V;

D+:USB D+;

D-:USB D-;

TXD:異步數(shù)據(jù)輸出(UART發(fā)送);

RXD:異步數(shù)據(jù)輸入(UART接收);

CTS:清除發(fā)送控制輸入(低電平有效);

RTS:準備發(fā)送控制輸出(低電平有效);

DSR:數(shù)據(jù)設置準備好控制輸出(低電平有效);

DTR:數(shù)據(jù)終端準備好控制輸出(低電平有效);

DCD:數(shù)據(jù)傳輸檢測控制輸入(低電平有效);

RI:振鈴指示器控制輸入(低電平有效);

SUSPEND:當CP2101進入USB終止狀態(tài)時該引腳被驅動為高電平;

:當CP2101進入USB終止狀態(tài)時該引腳被驅動為低電平;

NC:這些引腳應該為未連接或接到VDD的引腳。

CP2101內部及接口連接示意圖如圖4所示。本文引用地址:http://www.104case.com/article/190326.htm

2 FPGA內部邏輯設計

2.1 內部邏輯框圖

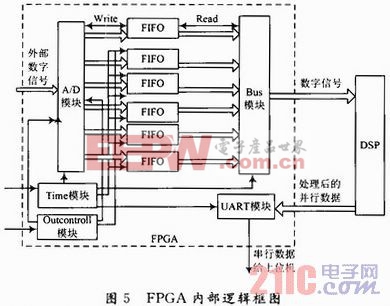

FPGA內部各個模塊的邏輯框圖如圖5所示。

2.2 主要邏輯設計

本設計系統(tǒng)中FPGA內部模塊主要有:Time模塊、A/D模塊、Outcontrol模塊、FIFO模塊、Bus模塊和UART模塊。其中,最主要的模塊為A/D模塊、FIFO模塊和UART模塊,下面就這三個模塊進行描述和實現(xiàn)。

評論