基于ARM和FPGA的靶場破片測速系統的設計

破片速度是戰斗部爆炸效能*估的一個重要參數。傳統的靶場破片測速系統多使用多路數據采集卡設置好的參數現場采集標靶的試驗波形,試驗完成后再交由計算機進行后期處理和解讀以獲取破片速度等參數。但隨著軍事科技的日新月異,靶場破片測速系統需要根據實際情況現場設置的參數越來越多,參數設置的靈活性越來越強,對系統工作的實時性要求越來越高;另一方面,戰斗部爆炸試驗在野外進行,條件惡劣,大型設備攜帶不便,以往的PC機+數據采集卡設計已經越來越不能滿足靶場試驗的要求。嵌入式系統具有功耗小、便攜性好、穩定性高、實時性強的特點,近年來隨著嵌入式技術的不斷發展,把嵌入式技術引入靶場破片測速系統設計中,為靶場破片測速系統設計提供了一個新的思路。

本文引用地址:http://www.104case.com/article/190254.htm本文設計的靶場破片測速系統以ARM處理器為控制核心,利用了FPGA強大的多路并行處理能力進行數據處理,在基于嵌入式Linux的平臺上采用Qt/Embedded設計了友好的人機交互界面。系統功能完善,操作直觀簡單,攜行方便,能夠滿足在野外進行破片測速的大多數需要。

1 系統硬件設計

ARM處理器選用SAMSUNG公司推出的基于ARM920T內核的S3C2440。S3C2440主頻高達400 MHz,完全能夠勝任系統工作要求。S3C2440集成了SDRAM和FLASH控制器,提供了串口,觸摸屏接口,USB接口等多種接口,接口豐富、功能強大,是一款高性能,低價格的處理器,在嵌入式設備中獲得了廣泛的應用。

FPGA(現場可編程門陣列)選用了Altera公司StratixⅡ系列的EP2S15芯片,該芯片器件密度可達到15600等效邏輯元(LE),能提供419Kb片內TriMatrix存儲器,多達12個DSP區塊共有48個(18×18 b)乘法器,用來實現高性能濾波器和其他DSP功能。支持多種高速外接存儲器接口,支持各種標準的I/O,高速差分I/O,具有強大的高速多通道并行處理能力。

系統使用該芯片64 MB SDRAM作為系統內存,64 MB FLASH用于Linux內核、文件系統、應用程序和試驗數據的存儲,為系統運行提供了充足的存儲空間。

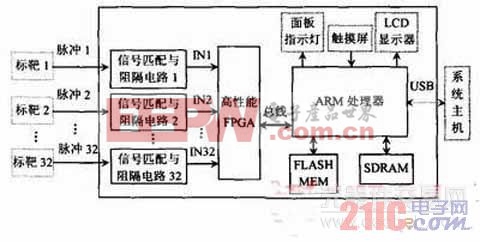

系統硬件結構圖如圖1所示。

圖1 系統硬件結構圖

在圖1中,系統采用了32個標靶用于破片測速,一個標靶對應FPGA的一個通道,每個通道對應一個32 b計數器。戰斗部爆炸后,破片擊穿標靶時產生的脈沖將作為起停信號,控制FPGA中相應通道的計數。所有通道中最早觸發的通道為基準通道,相應通道計數器值為0。從基準通道被觸發時刻起,除基準通道外所有通道計數器開始計數,直到本通道收到觸發信號或者最長計數時間時停止計數。停止計數時的通道計數值即為本通道的觸發計數值。

FPGA設置了32通道通斷寄存器、32通道輸入觸發器、通道觸發計數器等多個數據寄存器,用于保存標靶的通斷、觸發狀態及各個通道的觸發計數值;設置了最長記錄時間寄存器等多個控制寄存器用于控制FPGA的動作。經過處理,FPGA將標靶的通斷、觸發狀態及最終觸發計數值寫入相應數據寄存器中。

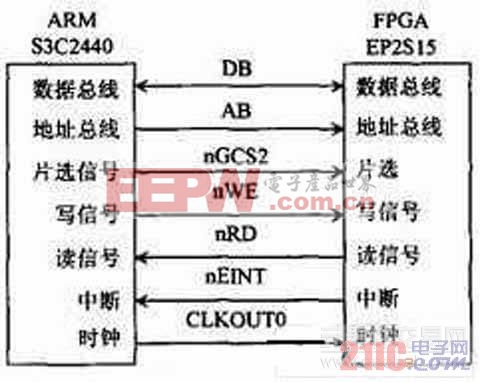

ARM處理器與FPGA通過總線方式實現通信。FPGA作為一個外部存儲器掛載在ARM的存儲器總線上,這樣ARM處理器通過存儲器指令可直接訪問FPGA,從而通過讀寫FPGA的數據和控制寄存器實現對FPGA的控制和對數據的讀取。

ARM與FPGA接口如圖2所示。

圖2 ARM與FPGA接口

評論