基于FPGA的無線信道模擬器設計

摘要:為了縮短研發周期,需要在實驗室模擬出無線信道的各種傳播特性,無線信道模擬器設計必不可少。采用基于頻率選擇性信道Jakes仿真器模型,使用Xilinx公司的VIrtex-2p模擬實現了頻率選擇性衰落信道,最后將數據通過串口上傳到Matlab分析信道的統計特性。

關鍵詞:無線信道;FPGA;Matlab;信道模擬器

0 引言

隨著人們對無線通信需求和質量的要求越來越高,無線通信設備的研發也變得越來越復雜,系統測試在整個設備研發過程中所占的比重也越來越大。為了更加方便地對所設計的系統進行調試和測試,無線信道模擬器是進行無線通信系統硬件測試不可或缺的儀器之一。目前,關于無線信道的模型研究比較多,而基于理論模型的硬件實現并不是很廣泛,同時成品十分昂貴,所以利用FPGA實現無線信道模擬器變得很有意義,節約了成本,而且也便于實現。FPGA是在PLD的基礎上發展起來的高性能可編程邏輯器件,使用FPGA進行數字邏輯設計,開發過程的投資較少,研制和開發的時間較短,并且因為引腳的可分配性電路一般比較簡單,修改和優化比較方便,并且在實際中易于使用。同時由于FPGA并行運算的特點,在大規模的數字運算中很有優勢,延時很小。

1 頻率選擇性衰落信道模型

多徑傳播信道的信道脈沖響應模式是模擬一個離散的廣義平穩非相關散射模型(WSSUS)。這樣的頻率選擇性衰落信道應該滿足兩個假設條件:

(1)在時間t(可能是幾個碼元長度)內,衰落的統計特性是平穩的;

(2)電波到達角和傳播時延是統計獨立變量。

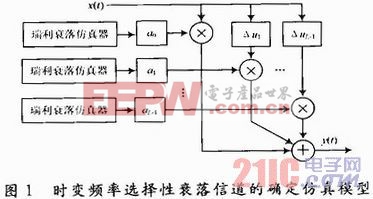

時變頻率選擇性衰落信道的確定仿真模型如圖1所示。

評論