基于FPGA的智能全數字鎖相環的設計

1 引言

本文引用地址:http://www.104case.com/article/190227.htm數字鎖相環路已在數字通信、無線電電子學及電力系統自動化等領域中得到了極為廣泛的應用。隨著集成電路技術的發展,不僅能夠制成頻率較高的單片集成鎖相環路,而且可以把整個系統集成到一個芯片上去。在基于FPGA的通信電路中,可以把全數字鎖相環路作為一個功能模塊嵌入FPGA中,構成片內鎖相環。

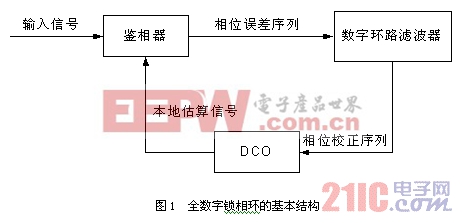

鎖相環是一個相位誤差控制系統。它比較輸入信號和振蕩器輸出信號之間的相位差,從而產生誤差控制信號來調整振蕩器的頻率,以達到與輸入信號同頻同相。所謂全數字鎖相環路(DPLL)就是環路部件全部數字化,采用數字鑒相器(DPD)、數字環路濾波器(DLF)、數控振蕩器(DCO)構成的鎖相環路,其組成框圖見圖1示。

當鎖相環中的鑒相器與數控振蕩器選定后,鎖相環的性能很大程度依賴于數字環路濾波器的參數設置。

2 K計數器的參數設置

74297中的環路濾波器采用了K計數器。其功能就是對相位誤差序列計數即濾波,并輸出相應的進位脈沖或是借位脈沖,來調整I/D數控振蕩器輸出信號的相位(或頻率),從而實現相位控制和鎖定。

K計數器中K值的選取需要由四根控制線來進行控制,模值是2的N次冪。在鎖相環路同步的狀態下,鑒相器既沒有超前脈沖也沒有滯后脈沖輸出,所以K計數器通常是沒有輸出的;這就大大減少了由噪聲引起的對鎖相環路的誤控作用。也就是說,K計數器作為濾波器,有效地濾除了噪聲對環路的干擾作用。

顯然,設計中適當選取K值是很重要的。K值取得大,對抑止噪聲有利(因為K值大,計數器對少量的噪聲干擾不可能計滿,所以不會有進位或借位脈沖輸出),但這樣捕捉帶變小,而且加大了環路進入鎖定狀態的時間。反之,K值取得小,可以加速環路的入鎖,但K計數器會頻繁地產生進位或借位脈沖,從而導致了相位抖動,相應地對噪聲的抑制能力也隨之降低。

為了平衡鎖定時間與相位抖動之間的矛盾,理想的情況是當數字鎖相環處于失步狀態時,降低K計數器的設置,反之加大其設置。實現的前提是檢測鎖相環的工作狀態。

3 工作狀態檢測電路

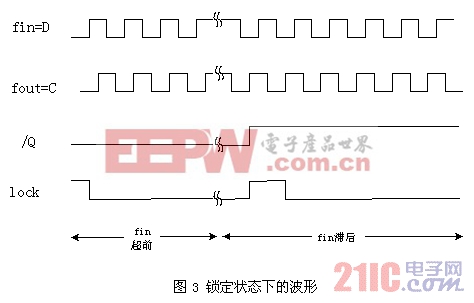

圖2為鎖相環狀態檢測電路,由觸發器與單穩態振蕩器構成,fin為輸入的參考時鐘,fout為鎖相環振蕩器輸出的時鐘移相900。fout對fin的抽樣送入單穩態振蕩器。

fpga相關文章:fpga是什么

數字通信相關文章:數字通信原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 數字濾波器相關文章:數字濾波器原理 鎖相放大器相關文章:鎖相放大器原理

評論