具有高阻抗并行接口和內部基準電阻的TLC5510解析方

3 基于FPGA的等效采樣

3.1 實現方案

該系統設計采用延遲法來實現等效采樣。如圖3所示,設輸入信號f(t)的周期為T(頻率為f),若將f(t)的一個周期T以△t等分,在時間t1進行第一次取樣,為了采集到下一個相位點,在時間t2進行第二次采樣,t1~t2可相隔多個信號周期。假設m個,則相鄰兩個采樣脈沖的時間間隔為(mT+△t)。如此類推,以下3個采樣點則分別在t3,t4,t5時刻采樣。在每個觸發位置延時N△t(N=0,1,2,3…)后存儲采樣,即可合成一個完整波形。這種方法控制方便,通過FPGA完成整個觸發、延時、采樣和存儲功能,但對觸發電路和延時電路要求很高。

3.2 硬件電路設計

3.2.1 整形觸發電路

由于每一次采樣都要由某一事件觸發,所以該系統設計采用內觸發,即觸發源為被采樣信號,并由硬件觸發電路實現。該電路可把各種波形的周期信號整形為與原信號周期相同的方波信號。

由于采用等效采樣技術,其被測信號頻率較高。假設被采樣信號的最高頻率約為10 MHz,則整形器件選用Maxim公司的電壓比較器MAX912。當輸入信號電壓高于預置的觸發電平時,輸出高電平;反之輸出低電平。

3.2.2 采樣保持電路

每次采樣是比觸發時刻延遲N△t的數據點,但由于被采樣信號頻率很高,要準確采樣到該點基本無法實現。為此需要引入采樣保持電路。

采樣保持電路的功能:在采樣時刻到來之前,該模塊的輸出電壓隨輸入電壓變化。當到達采樣時刻時,輸出電壓保持不變。以供TLC5510采樣。

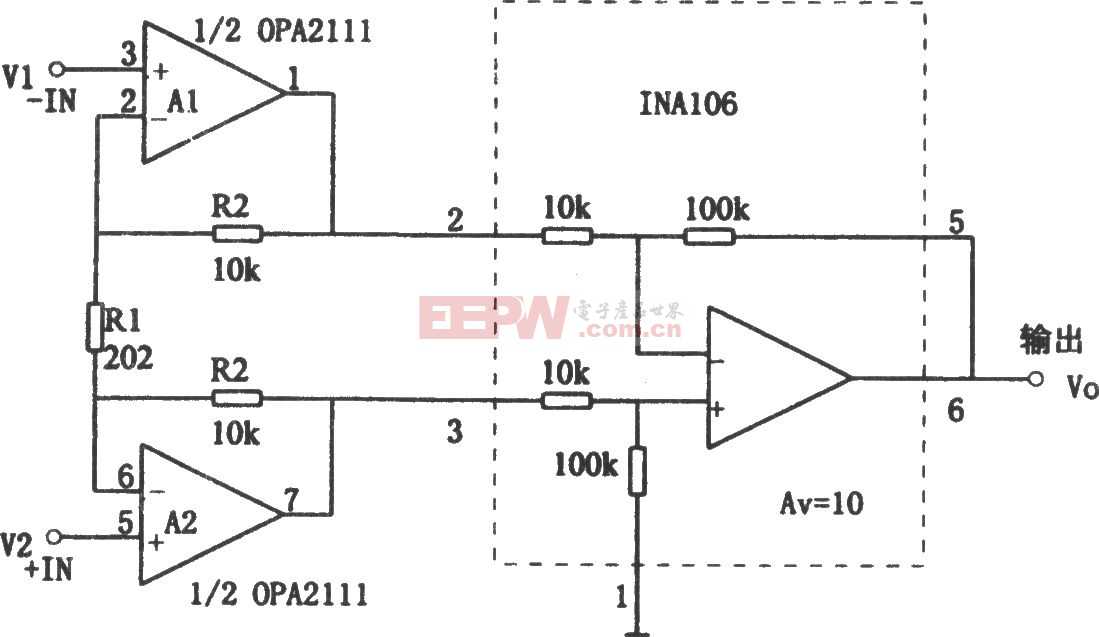

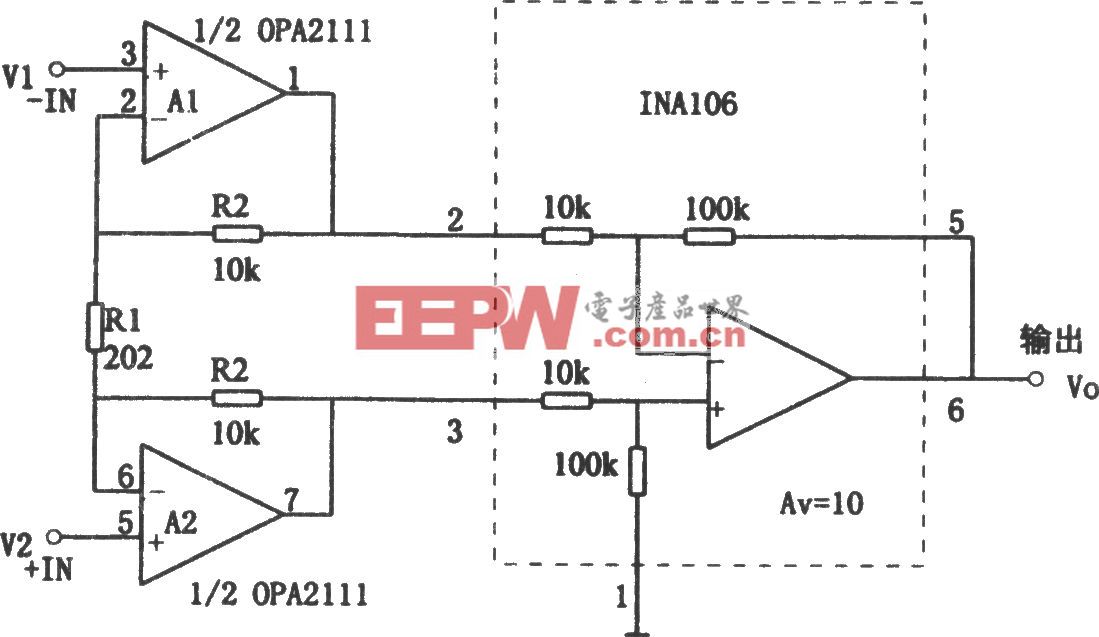

該采樣保持電路由兩片運算放大器A1,A2和模擬開關A3構成,采樣時通過FPGA控制時鐘使A3的通道S1導通。A1,A2為單位增益的電壓跟隨器,故Uo=Uc=Uo,此時電容充電至Uc。因電壓跟隨器的輸出電阻很小,故電容快速充電。斷開S1,由于Uc無放電通路,其電壓基本不變,故Uo保持不變,即保存采樣結果。

3.3 軟件編程控制

等效采樣的軟件控制實際上是指對采樣時刻的控制和對外同采樣保持電路時序的控制,該控制可以在FPGA內部編程實現,對應的實現模塊如圖6所示,主要由兩部分組成。其一為數字鎖相環(PLL),用于產生頻率足夠高的脈沖信號。由于采樣率與△t有關,因此將原來FPGA自帶的40 MHz時鐘信號送入數字鎖相環使之5倍頻,進而提高至200 MHz。其二為控制模塊,采用同步開啟異步復位的編程思想。它有兩個時鐘輸入端:clkce2是被測信號經整形電路后的脈沖信號,該信號為同步信號,也為觸發源。每次采樣都由該信號觸發開始計數;clk_200是數字鎖相環產生的高頻采樣脈沖,計數開始后內部計數器對clk_200計數,當計數到m后(即m△t時間),計數完畢,馬上控制采樣保持電路進入保持狀態,然后在經過若干個clk_200時鐘周期后(為了使信號完全進入保持狀態電平達到穩定),采樣該數據點(每一數據點代表一個相位的數據值)。若每一個采樣周期需要采樣256個點,則最大延時為256△t=256/200=1.28μs,而被測信號為10 MHz,其周期為0.1μs,所以兩采樣點之間至少要間隔13個周期。

4 結束語

采用傳統的實時采樣方法可對頻率低于1 MHz的信號進行采樣,而對于頻率較高的信號,則介紹的基于FPGA的等效采樣技術,能使得TLC5510對高頻信號采樣,TLC5510應用更加廣泛。

評論