LVDS信號的PCB設計和仿真分析

2.1 PCB板疊層設計

使用Cadence16.3的SI工具進行信號完整性的仿真。

設計采用6層板的疊層結構,經(jīng)過合理安排疊層厚度,通過Allegro計算,表面微帶線寬6 mil線間距6 mil時,阻抗理論計算值分別為103和99.4 Ω。符合阻抗控制要求。內(nèi)層沒有走差分線,線寬設置為5 mil。本文引用地址:http://www.104case.com/article/190197.htm

2.2 LVDS差分對的波形分析

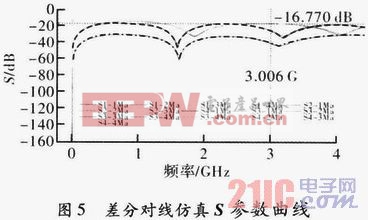

LVDS信號線之間的等距是為保證兩者差分阻抗一致,減少反射。差分對的兩條線之間要保持平行,防止耦合共模干擾。在疊層設置中,保持平行是為了保持阻抗連續(xù),否則會產(chǎn)生延遲和抖動。通過S參數(shù)分析差分對阻抗(Differential Impedance)。從仿真如圖3所示,S11在0~3.0 GHz的頻域范圍內(nèi),其最劣化的指標為:-16.770 dB以下,S22(虛線的曲線)也不劣于-17 dB。這說明該差分對的差分阻抗連續(xù)性很好。

通過Hspice的IN,OUT仿真,可以看出差分對良好的對稱性。

3 結束語

LVDS在航天軍工等方面具有廣泛的應用,但是由于信號完整性的問題考慮不夠,經(jīng)常出現(xiàn)設計問題,文中從基于LVDS的高速信號下載器的約束設計進行論述,通過仿真研究,達到了設計目的。

評論