單片機與FPGA實現等精度頻率測量和IDDS技術設計方

1.1.2 相位部分

相位寄存器的輸出通過相位調制器與相位控制字K相加,使最終的輸出產生一定的相位偏移θ,θ的值與相位控制字K與ROM中的數據有關。我們通過設置兩路信號的K值,使兩路信號有不同的相位偏移量,從而產生相位差△θ。設A路信號的控制字為K,B路信號的控制字為K’,考慮到FPGA的內部資源,取512個采樣點,可得

通常我們只要改變控制字K就可以實現步進調整。

1.2 DDS產生的軟件設計

1.2.1 FPGA軟件設計

FPGA負責接收由單片機送過來的頻率字與相位控制字,同時將波形在ROM中的數據送給DA轉換器進行DA轉換,輸出正弦波、方波、三角波三種波形,通過調節DA轉換器的基準電壓可調節輸出的正弦波、方波、三角波三種波形的幅度,利用按鍵可以設置一定范圍內的頻率值和步進值,并能實現波形間的任意切換,實現了頻率、步進、幅度的任意調節。

1.2.2 單片機軟件設計

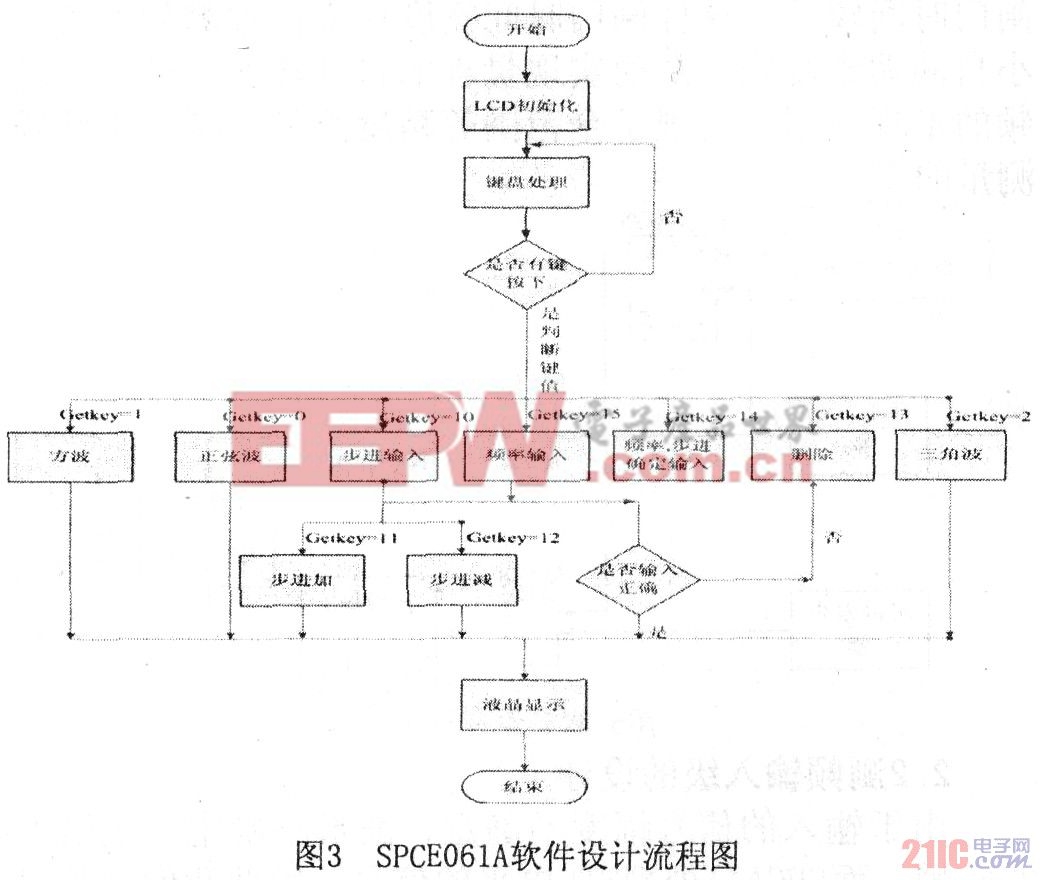

單片機軟件設計主要是負責接收鍵盤置入的頻率、步進值、選擇波形并將其在液晶顯示屏中顯示和把各種控制信號和數據送到FPGA中。可設置任意頻率、任意步進、波形切換等多種輸出方式,在此基礎上可擴展為任意信號發生器,具體程序流程圖如圖3:

1.2.3 FPGA與單片機的通信

本系統設計中,FPGA與凌陽單片機采用串行輸入并行輸出的方式進行通信。使用VHDL語言在EP2C20器件中利用D觸發器和移位寄存器接收凌陽單片機發送過來的頻率控制字和相位控制字,然后送入相位累加器。在FPGA與凌陽單片機通信中,單片機實行串行輸入,不斷地向FPGA送頻率控制字和相位控制字,送給FPGA實現相位累加。

評論