基于FPGA和FLASH ROM的圖像信號發(fā)生器設(shè)計

2.2 FLASH ROM無效塊管理

選取 SAMSUNG 公司的 NAND 型的K9F1G16UOM-FLASH作為存儲芯片,單片容量為1 Gb、數(shù)據(jù)寬度為16 b。大容量的FLASH器件一般都是按塊(block)管理其存儲空間。FLASH芯片可能有包含一個或多個無效位的無效塊,這在NAND型FLASH中是不可避免的。無效塊出現(xiàn)的幾率很小,但影響很大。如果對FLASH中的無效塊進行操作,無效塊會在數(shù)據(jù)記錄的過程中造成數(shù)據(jù)的丟失和誤碼,影響數(shù)據(jù)的有效性和完整性。由于無效塊和有效塊相互隔離,無效塊并不會影響有效塊的操作,因此只要在數(shù)據(jù)存儲前將FLASH中的無效塊剔除,就可有效避免數(shù)據(jù)的丟失和誤碼。

FLASH在出廠時會對無效塊進行檢查,并將信息標(biāo)注在FLASH每一塊的第一頁和第二頁的第1 024個字,0xFFFF表示塊有效。非0xFFFF則表示無效塊。為避免破壞這些標(biāo)注信息,在對FLASH進行任何擦除或?qū)懭氩僮髑埃紫冉o效塊信息表。SAMSUNG公司保證其FLASH的第一塊一定是有效塊,并且在對其擦寫1 000次以內(nèi)不會出任何錯。所以本文使用該塊來保存整片F(xiàn)LASH的無效塊信息。FPGA遍歷訪問FLASH中的每個塊的第一頁和第二頁,判斷該塊是否滿足有效塊的要求,若不滿足則將其塊地址緩存到FPGA的RAM中;接下來,將FLASH的無效塊數(shù)量和無效塊地址存入該片F(xiàn)LASH的第一塊的第一頁內(nèi)。在FLASH的使用過程中,仍然有可能產(chǎn)生新的無效塊,當(dāng)出現(xiàn)這種情況時,則需要更新無效塊信息表。無效塊信息表用來供讀寫地址產(chǎn)生器查詢時使用,這樣就可以避開壞塊的影響。

2.3 數(shù)據(jù)寫入管理

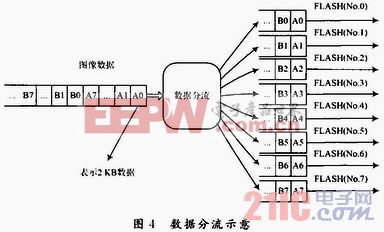

圖像數(shù)據(jù)寫入時,FPGA接收來自USB控制器的數(shù)據(jù),并產(chǎn)生控制時序?qū)?shù)據(jù)寫入FLASH。由于高幀頻相機一般是多通道輸出,所以在模擬這類相機的時候要注意這個因素。對于某一幅目標(biāo)圖像,圖像數(shù)據(jù)寫入首先是應(yīng)用程序獲取圖像數(shù)據(jù);然后將各個通道對應(yīng)位置的像素數(shù)據(jù)按次序調(diào)整在一起;接著通過USB將數(shù)據(jù)傳輸至FPGA,F(xiàn)PGA將數(shù)據(jù)截斷成2 KB大小并依次將各分段數(shù)據(jù)塊寫入8片F(xiàn)LASH中,數(shù)據(jù)分流如圖4所示。圖像數(shù)據(jù)按通道進行調(diào)整可以使得系統(tǒng)輕松地實現(xiàn)多通道輸出。對數(shù)據(jù)的分流處理,使得系統(tǒng)的8片F(xiàn)LASH在讀出時可以真正實現(xiàn)并行讀取數(shù)據(jù)。本文引用地址:http://www.104case.com/article/190175.htm

FLASH的一頁(page)的大小為2 KB,也是它的基本瀆寫單元。要想連續(xù)寫入2 KB的數(shù)據(jù),需要將訪問FLASH的頁地址都設(shè)為00H。當(dāng)FPGA需要向某一片F(xiàn)LASH寫入數(shù)據(jù)時,首先要查看該片F(xiàn)LASH的FPGA寫入管理模塊是否處于ready狀態(tài);若處于busy狀態(tài),則應(yīng)用程序進入傳輸?shù)却?dāng)寫入管理進入ready狀態(tài)后,則應(yīng)用程序發(fā)送數(shù)據(jù),一共2 KB數(shù)據(jù)緩沖到FLASH在FPGA中對應(yīng)的RAM;數(shù)據(jù)緩沖完成之后,該FLASH的寫入管理模塊進入busy狀態(tài)并開始將RAM中的數(shù)據(jù)寫入FLASH ROM的某一頁(page),同時FPGA轉(zhuǎn)向?qū)ο乱黄現(xiàn)LASH進行傳輸訪問。

2.4 數(shù)據(jù)讀出管理

數(shù)據(jù)讀取輸出是指FPGA模擬CCD相機輸出時序,將FLASH中的數(shù)據(jù)通過Camera Link接口進行循環(huán)輸出。所選的FLASH的單片最大讀出速率可達(dá)25 MB/s,由于8片F(xiàn)LASH可以并行讀出,所以整個系統(tǒng)的數(shù)據(jù)讀出率可以達(dá)到200 MB/s。這樣有利于模擬出較高幀頻的CCD相機輸出。當(dāng)系統(tǒng)進行圖像數(shù)據(jù)瀆取輸出時,F(xiàn)PGA中設(shè)置了FIFO來緩沖數(shù)據(jù)。Camera Link輸出管理模塊產(chǎn)生相機時序,將FIFO中的數(shù)據(jù)按要求送到Cam era Link接口。對于從FLASH向FIFO轉(zhuǎn)移數(shù)據(jù),首先將各FLASH中的2 KB數(shù)據(jù)被讀入其在FPGA中對應(yīng)的RAM中;然后控制各RAM中的數(shù)據(jù)被按順序轉(zhuǎn)移至FIFO中,控制器通過FIFO的數(shù)據(jù)深度來判斷是否需要繼續(xù)讀入數(shù)據(jù),當(dāng)判斷FIFO中的數(shù)據(jù)快滿時暫停讀取,這時由于數(shù)據(jù)繼續(xù)被讀出,隨著FIFO中的數(shù)據(jù)減少到一定程度時,啟動將RAM中的數(shù)據(jù)繼續(xù)讀入FIFO;一旦一個RAM中的數(shù)據(jù)被轉(zhuǎn)移,則FLASH讀取管理模塊繼續(xù)將該FLASH中的后續(xù)數(shù)據(jù)寫入該RAM。

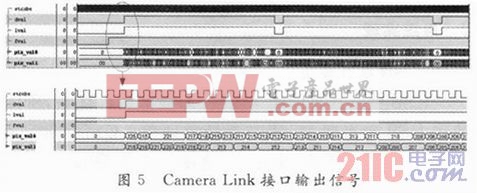

在加載某種8位數(shù)據(jù)寬度、雙通道輸出的目標(biāo)圖像時,使用Chipscope得到的Camera Link信號如圖5所示。其中,strobe為時鐘信號,dval,lval,fval分別是數(shù)據(jù)有效、行有效、幀有效信號。觀測結(jié)果說明輸出的數(shù)據(jù)與加載的數(shù)據(jù)保持一致,輸出控制時序也符合要求。

為了模擬出不同類型的CCD相機,只需要修改FPGA程序中設(shè)定的strobe時鐘頻率、Line blanking時間、Frame blanking時間等必要參數(shù)即可。

評論