星載環境FPGA軟件在軌重加載的一種方法

2 硬件電路設計

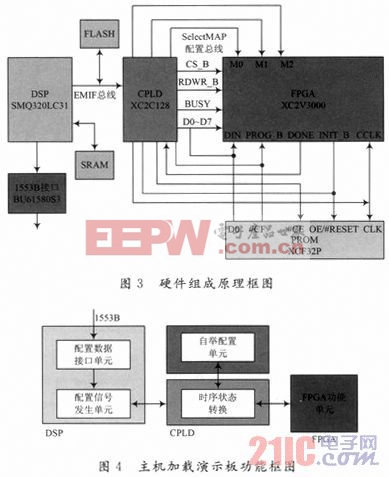

本系統硬件組成原理框圖見圖3,主控DSP芯片選用TI公司SMQ320LC31,通過1553B接口實現與星上控制計算機的通信,FPGA選用XILINX公司VIRTEX-Ⅱ系列芯片XC2V3000,其配置芯片選用XCF32P,DSP通過CPLD實現對FPGA加載模式的控制。本文引用地址:http://www.104case.com/article/190121.htm

圖3所示的電路框圖可以分為以下功能模塊:配置數據接口單元、配置信號發生單元、時序狀態轉換、自舉配置單元、FPGA功能單元,其邏輯關系如圖4所示。

各功能單元的功能和性能描述如下:

(1)配置數據接口單元:該單元通過1553B接口從星上控制計算機接收FPGA配置數據。

(2)配置信號發生單元:該單元產生配置FPGA所需的配置數據和時序。

(3)狀態時序轉換單元:該單元一方面實現FPGA配置方式的狀態切換:自舉配置;另一方面將配置信號發生單元產生的信號轉換成FPGA配置接口所需的信號。

(4)自舉配置單元:即PROM,保存預先裝好的FPGA配置數據。

(5)FPGA功能單元:即FPGA,接收來自于PROM的配置數據或者來自于DSP(經過CPLD轉換)的配置數據。

該系統在實際工作過程中,通過DSP和CPLD的靈活控制,可以實現多種配置模式的切換:

(1)上電過程直接通過PROM對FPGA進行配置加載;

(2)上電過程直接通過DSP片外FLASH對FPGA進行配置加載;

(3)DSP實時接收星上控制計算機傳送的配置數據,實現對FPGA的配置加載;

(4)DSP實時接收星上控制計算機傳送的配置數據,將其燒寫至PROM;

(5)DSP實時接收星上控制計算機傳送的配置數據,將其燒寫至FLASH。

3 軟件設計

3.1 DSP軟件設計實現

系統上電之后,DSP上電后,首先進行狀態檢測,判斷上電時是PROM串行加載還是FLASH并行加載。然后,星上控制計算機通過1553B接口向DSP傳送FPGA配置數據,并發送配置模式控制命令,DSP根據接收的命令選擇配置方式,按照配置時序向CPLD的相應寄存器寫配置數據以及配置控制信號。

DSP軟件功能框圖如圖5所示,軟件主要完成兩個功能:功能一為完成1553B接口數據的傳輸,并存儲到SRAM中,然后根據1553B接口的控制命令決定進行配置的方式或者轉存到FLASH中;功能二為模塊根據命令和FPGA配置時序產生配置信號,并輸出給CPLD配置寄存器。

整個DSP軟件程序包含以下幾個主要函數:1553B接口數據傳輸和處理函數、FLASH擦除與裝訂函數、SelectMap配置函數和中斷處理函數。軟件從main函數入口開始運行,進行相應的初始化設置和配置,并開啟中斷,然后進入無限循環狀態,等待外部中斷的到來并進行相應的中斷服務處理。詳細軟件流程圖如圖6所示。

評論