星載環境FPGA軟件在軌重加載的一種方法

摘要:FPGA在空間系統中已經廣泛應用,為了滿足系統可靠性和可擴展性的要求,實現FPGA軟件的在軌重加載迫在眉睫。根據FPGA的加載配置原理,以Xilinx公司的Virtex-Ⅱ系列FPGA為實例,介紹了FPGA在軌重加載的硬件電路設計以及軟件設計。經過實驗室測試驗證,該設計方法合理可行,滿足星載環境下FPGA軟件在軌編程及重加載的設計需求。

關鍵詞:FPGA;在軌重加載;在軌編程;星載環境

0 引言

FPGA已經廣泛應用于星載信號處理系統中,然而其在空間環境中的可靠性設計是一個難題。一方面,FPGA軟件可能受到外部空間環境影響而產生各種問題,特別是單粒子效應造成的FPGA程序出錯,其導致的后果是嚴重的甚至是災難性的;另一方面,當FPGA軟件本身存在設計缺陷或者由于衛星系統改變應用需求時,若能實現星載環境下FPGA軟件的遠程更新升級,其軟件系統的生命周期便可以得到延長,同時產生的經濟效益也是不可估量的。

為此,本文介紹一種星載環境下FPGA軟件在軌重加載的方法,通過星上系統的1553B接口接收FPGA配置數據文件,在DSP和CPLD的控制下,靈活地實現FPGA程序的在軌編程及重加載。

1 FPGA加載原理

基于SRAM工藝的FPGA由于在掉電后配置數據丟失,因此需要在上電后對其進行加載,而配置數據被保存在外部的非易失存儲器中。

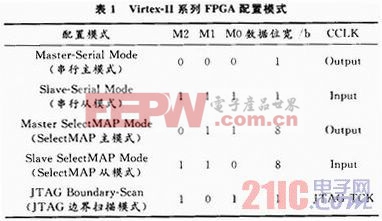

Xilinx公司的Virtex-Ⅱ系列FPGA通過芯片配置管腳MODE PIN(M0,M1,M2),可以實現5種配置模式,詳見表1。

上述5種模式中,JTAG邊界掃描模式具有最高的優先級,其加載方式是通過專用JTAG口對FPGA進行訪問。SelectMAP模式實際上就是并行模式,其加載時的數據訪問位寬為8 b,加載過程與串行模式相同。主模式和從模式的區別在于時鐘是由FPGA自身提供,亦或是外部提供,當FPGA主動輸出時鐘時即為主模式,反之即為從模式。

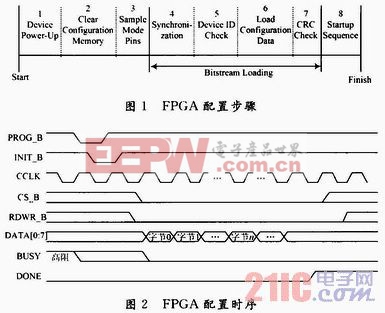

FPGA的配置過程如圖1所示,主要由3個階段8個步驟組成。FPGA在Slave SelectMAP模式下配置過程中使用的信號包括:PROG_B,INIT_ B,CCLK,CS_B,RDWR_B,DATA[0:7],BUSY,DONE,其時序關系如圖2所示。

根據圖1和圖2,Slave SelelctMAP模式下,FPGA加載過程描述如下:

第1階段:啟動和初始化,分為3個步驟:

FPGA上電正常后,通過PROG_B引腳低脈沖進行FPGA異步復位,使得FPGA內部邏輯清零;PROG_B拉高后,停止外部復位,INIT_B引腳會在自動產生一個由低到高的跳變,指示FPGA內部初始化完成,可以進行數據下載;FPGA檢測其專用的配置模式管腳M0~M2的電平,從而確定加載模式。

第2階段:比特流加載,分為4個步驟。INIT_B信號變高后,不需要額外的等待時間,Virtex器件就可以立即開始數據的配置。比特流數據在外部CCLK信號上升沿按字節方式置入。其中的Synchronization(同步)、Device ID Check(檢測器件ID號和配置數據中的ID號是否匹配)、Load Configuration Data(下載數據流)和CRCCheck(CRC校驗)對用戶是完全透明的,同步字、配置數據中ID號和CRC校驗和都是在生成配置數據文件時和配置數據一起打包,嵌入在配置數據文件當中。

第3階段:Startup啟動。在成功校驗CRC碼位后,FPGA進入Startup狀態。它是由8相狀態機實現的,中間包括等待DCM鎖相、DCI匹配等幾個狀態,最后FPGA釋放外部DONE引腳,對外輸出高阻態,由外部上拉高,指示FPGA加載成功。

評論