基于FPGA視頻圖像的Canny算法加速器的設計

2.2 加速器的地址產生

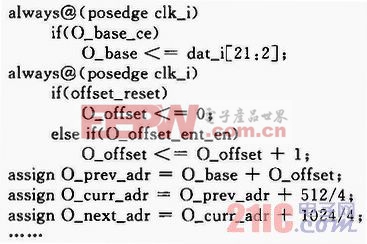

在系統的連續處理過程當中,加速器沒有專門的等待時間用來對數據進行讀取和存儲,這兩類運算都是并行進行的。因此加速器需要具有自動選通的讀/寫地址電路。對于一幅512×512圖像來說,從偏移值0開始計數,一次加1,以便于從內存中讀一組4個像素值,把偏移地址和基地址加起來形成前一行的像素地址,把它加上512/4就形成當前行的讀地址,再加上1 024/4就形成了下一行的讀地址。對于寫地址來說,從偏移值512/4開始計數,一次加1形成每次的寫地址。地址發生器的部分代碼如下:

3 Canny算法加速設計

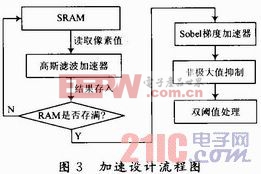

為了使得整個算法的計算速度得到提高,使算法既滿足高速要求也不會耗費大量的硬件資源,本文對高斯濾波和梯度強度計算兩個任務模塊做了加速設計組合,流程圖如圖3所示。本文引用地址:http://www.104case.com/article/190119.htm

高斯濾波器采用與Sobel加速器相似的設計原理,具有流水線的加速功能。圖中RAM是FPGA中自帶的Block RAM塊,其大小配置為僅存儲當前被處理圖像的三行像素值,對于512×512的8位圖像來說RAM應配置為512×3×8 b。因為高斯濾波的存儲和Sobel加速器在讀取的時候都是每4個像素點即32 b數據來進行,所以配置為32位寬的同時讀寫操作的雙口RAM。

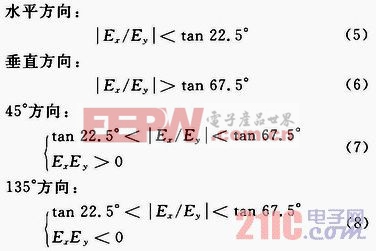

梯度運算之后,進行非極大值的抑制,在非極大值抑制之前需要計算梯度的方向。梯度方向的計算分為四個方向:水平、垂直、45°方向及135°方向,且每個方向上都包含兩個45°的范圍。通過Ex和Ey的比值及正負可以確定梯度方向落在上面規定的四個方向之一。判斷四個方向的具體如下:

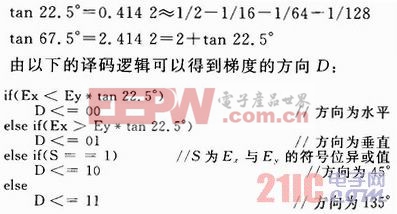

在FPGA中,直接做除法運算是很復雜的過程;為了減少資源的開銷,把式(5)~式(8)中的除法變換成乘法,再做比較來判斷梯度的方向。對于tan 22.5°和tan 67.5°做如下處理:

非極大值的抑制在系統中通過選擇器和比較器來實現。根據輸入的梯度值和梯度方向,用非極大值抑制條件(式(5)~(8))和高低閾值條件對輸出的數據進行比較選擇,強邊緣點輸出為255,弱邊緣點輸出為0。由于硬件流水線的特點,邊界像素的計算結果是無效的,所以將邊界上的行列都置為0。重復以上步驟,直到整幅圖像掃描完成,最終得出邊緣圖像。

fpga相關文章:fpga是什么

評論