2.1 三線制同步串行通信控制器IP核接口描述

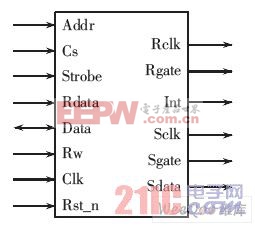

本設計最終實現的目標是生成如圖2所示的IP核接口封裝��。

圖2 三線制同步串行通信控制器IP 核接口封裝圖

其中���,三線制同步串行通信控制器IP核接口信號定義如表1所示����。該IP核共有全局信號管腳8個,接收接口信號管腳和發送接口信號管腳各3個����。

表1三線制同步串行通信控制器IP核接口信號描述

2.2 三線制同步串行通信控制器IP核電路結構設計

按照設計目標���,根據需要實現的功能��,可將三線制同步串行通信控制器結構劃分成幾個大的功能模塊,這些模塊獨自完成一定的任務��,結合起來實現通信控制器的整體功能���。同時���,劃分模塊功能后�����,可以更方便地用硬件描述語言VHDL對其進行描述。

評論