基于FPGA 的多時鐘片上網絡設計

(1)緩沖部分或者全部到來的數據包,以及當下游開關可以用時,傳送頭部及緊跟的flit。

(2)劃分路由器核心以及路由器的頻率,從而支持一個多時鐘的網絡設計。

(3)通過仲裁器監察write_count 端口的信息,來實現支持可變化大小的數據包。在緩沖區有單獨時鐘域的情況時, 就需要一種有效的方式實施完整的或者空的邏輯。通過以下方式使控制信號同步:

(1)發送數據包粒度作為一小部分FIFO 的空間。

(2) 在一個時鐘周期內, 一個連接終止之前設置flit 的尾部位。在所使用的FPGA 設計中,由于支持FIFO 的最小深度是16, 所以它適合于在虛擬直通中緩沖整個數據包。write_count 的空和滿狀態信號將集成在FIFO 中。在一個多數據包的緩沖區中加大存儲flit 的能力,將有助于提高FIFO 的利用率。此外,獲得網絡的吞吐量的增益,是由于上游連續包釋放緩沖區所促成的。

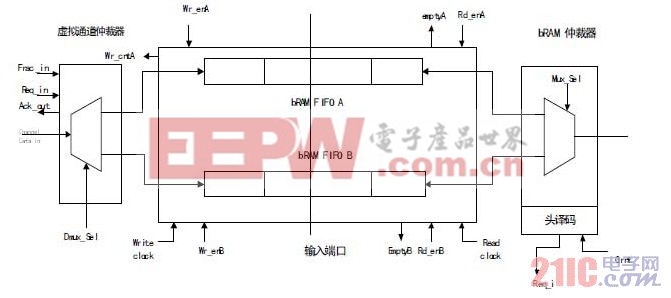

圖1 輸入端口設計圖

bRAM 仲裁器: 輸入端口還包含了控制邏輯作出的仲裁決定。當選擇一個非空的bRAM 時, 簡單的Round-robin 的方式仲裁算法將會啟用。當選擇bRAM時,FSM 將會送出頭部flit,解碼出它的目的地址,并發送相應的要求。在所設計的路由器中采用XY 路由算法將大大簡化了解碼器的邏輯結構。根據XY 路由算法的通行路徑許可,即將釋放的請求線將會減少。

頭譯碼器:在XY 路由算法中,頭數據片一開始往X 軸方向走,當到達X 軸所在的目標地址時,就會往Y方向走。所有緊隨著的數據片將以流水線的方式跟著頭數據片移動。這種簡便的XY 路由算法適用于減化頭解碼器、交叉點矩陣以及中央仲裁器的邏輯結構。以上簡化得邏輯結構將使FPGA 的芯片數顯著減少。

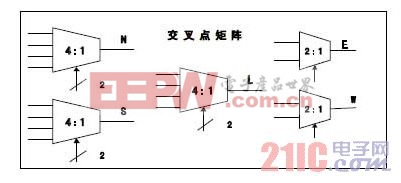

2.3 交叉點矩陣

設計一個多路交叉點矩陣, 目的是為了減少面積的使用。而另一種設計是支持復分解虛擬通道的交叉點連接。后一種方法,產生高網絡吞吐量,但要增加一個重要的復雜性開關。交叉點支持并行連接,以及被用于通過中央仲裁器支持多個信號同時請求。并非所有的交叉點連接都是使用XY 路由算法。經過邏輯優化,如圖2 所示設計中實施簡單的4 和2 輸入多路復用器開關(分別是L、N、S、E 以及W 端口)。上述優化方案減少了交叉點面積,使其使用的切片只有32 片。因此,達到路由器面積顯著減小的目的。

圖2 交叉點矩陣

輸入端口的分配方式將采用簡單的Round-robin仲裁機制。對上一次接收過的或沒有用到的端口將給予最低優先級,并排在隊列的最末端。將通過以下的方式提高路由器的性能:

(1)降低中央仲裁器的邏輯復雜度;

(2)盡量集中仲裁器,以減少req/grant 信號的數量。

在設計中減少邏輯復雜度以及布線, 從而減少數據堵塞,達到提高性能以及減低功耗的效果。

評論