基于FPGA的軟件無線電平臺設(shè)計

提取用戶窄帶信號進(jìn)行抽取由專用ADC芯片完成,數(shù)字下變頻部分由FPGA中的IP(Intellectual Property)模塊完成。用專用芯片進(jìn)行模數(shù)轉(zhuǎn)換可以提高系統(tǒng)的穩(wěn)定性和可靠性;用IP模塊完成數(shù)字下變頻功能可以降低功耗,提高速率。

數(shù)字下變頻后進(jìn)行解調(diào),經(jīng)過解調(diào)后的信號為一個比特流序列,比特流處理部分需要完成信息的加密解密、編碼譯碼等。如圖1所示,這部分功能可以用Verilog-HDL語言編寫DSP處理模塊完成,也可以用Matlab的FDATool進(jìn)行設(shè)計后自動生成Verilog-HDL源代碼和PowerPC指令程序;本文采用Verilog-HDL直接編寫DSP模塊的辦法,這樣可以對硬件處理流程進(jìn)行更好的掌控,并且獲得更高的信號處理性能。由于將DSP模塊嵌入FPGA中,通過增加或減少DSP邏輯電路可以使得設(shè)計更加靈活,例如可以將2FSK調(diào)制解調(diào),F(xiàn)IR濾波和FFT分別封裝成為單元模塊,編寫地址驅(qū)動后PowerPC程序執(zhí)行時可直接進(jìn)行調(diào)用,相比DSP專用處理器僅調(diào)用乘法器和移位寄存器的方法可以節(jié)省上百個指令周期,大大提高了實(shí)時信號處理的能力,具有在高端領(lǐng)域廣闊的應(yīng)用前景。

比特流序列處理完成后,可將數(shù)據(jù)傳入主機(jī)磁盤陣列經(jīng)行儲存,PowerPC通過PCI橋控制本系統(tǒng)和主機(jī)的數(shù)據(jù)傳輸,以滿足未來數(shù)據(jù)回放和可視化界面要求。

1.2 ADC模數(shù)轉(zhuǎn)換

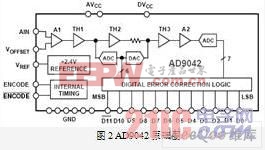

軟件無線電要求ADC,DAC盡可能的靠近天線,這需要很高的ADC的采樣率,采樣精度,動態(tài)范圍等特征[11~13]。AD9042是一款高性能高速ADC芯片,采用的是兩級子區(qū)式轉(zhuǎn)換結(jié)構(gòu),這種設(shè)計既保證了所需的轉(zhuǎn)換精度和轉(zhuǎn)換速度,又降低了功耗,同時也減小了芯片尺寸,AD9042系統(tǒng)原理如圖2所示[10]。AD9042可以保證的最小采樣率可達(dá)41MHZ, 12bit精度,80dB無寄生動態(tài)范圍。

1.3 DDS直接頻率合成

由于數(shù)字信號處理的處理速度有限,往往難以對A/D采樣得到的高速率數(shù)字信號直接進(jìn)行各種類別的實(shí)時處理。為了解決這一矛盾,需要采用數(shù)字下變頻技術(shù),將采樣得到的高速率信號變成低速率基帶信號,以便進(jìn)行下一步的信號處理。數(shù)字下變頻技術(shù)在軟件無線電和各類數(shù)字化接收機(jī)中得到了廣泛應(yīng)用。寬帶數(shù)字下變頻器基于外差接收機(jī)的原理,包括數(shù)字混頻、低通濾波、抽取三個環(huán)節(jié)[12]。抽取后得到和信號帶寬匹配的基帶抽樣信號,實(shí)現(xiàn)從寬頻帶中提取窄帶信號的目的。Xilinx提供的專用DDS(Direct DIGItal Synthesizer) IP模塊用以實(shí)現(xiàn)數(shù)字下變頻功能。

1.4 CPU控制單元

Virtex-4 FX系列FPGA集成了運(yùn)行速度高達(dá)450 MHz的雙32位嵌入式PowerPC,每個處理器可提供超過700 DhrySTone MIPS的性能,是普通FPGA中處理器性能的三倍。兩個完全集成的UNH認(rèn)證的10/100/1000 Ethernet MAC進(jìn)一步提升了Virtex-4 FX處理平臺的性能,從而提高了FPGA資源的可用性。本系統(tǒng)以PowerPC作為該系統(tǒng)的指令處理和控制單元,可以避免純硬件設(shè)計復(fù)雜,通用性差和不容易協(xié)調(diào)控制的缺點(diǎn)。PowerPC是本系統(tǒng)SoPC架構(gòu)的核心組成部分,擔(dān)負(fù)算法實(shí)現(xiàn)和中央控制兩部分任務(wù)。Virtex-4 FX內(nèi)部有大量乘法器可供調(diào)用,能夠充分滿足各種數(shù)字信號處理要求;PowerPC與前文提到用Verilog-HDL 設(shè)計的DSP模塊連接,使整個系統(tǒng)具有實(shí)時動態(tài)信號的處理能力。PowerPC作為控制器的狀態(tài)流程如圖3所示。

評論