基于FPGA 的UART 擴(kuò)展總線設(shè)計(jì)和應(yīng)用

2.2 UART 的邏輯設(shè)計(jì)

UART 的通信協(xié)議十分簡(jiǎn)單,以低電平作為起始位,高電平作為停止位,中間可傳輸 5~8 比特?cái)?shù)據(jù)和1 比特奇偶校驗(yàn)位,奇偶校驗(yàn)位的有無(wú)和數(shù)據(jù)比特的長(zhǎng)度由通信雙方約 定。一幀數(shù)據(jù)傳輸完畢后可以繼續(xù)傳輸下一幀數(shù)據(jù),也可以繼續(xù)保持為高電平,兩幀之間 保持高電平,持續(xù)時(shí)間可以任意長(zhǎng)。

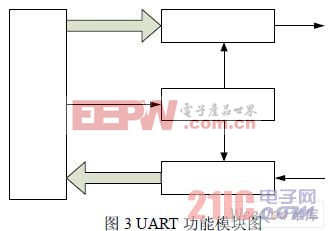

UART模塊由SLAVE接口、波特率控制器、UART接收器和UART發(fā)送器構(gòu)成。SLAVE 接口是為了實(shí)現(xiàn)WISHBONE 總線和功能模塊之間的數(shù)據(jù)傳輸;UART 發(fā)送器的用途是將準(zhǔn)備輸出的并行數(shù)據(jù)按照基本UART 幀格式轉(zhuǎn)為TXD 信號(hào)串行輸出;UART 接收器接收RXD 串行信號(hào),并將其轉(zhuǎn)化為并行數(shù)據(jù),但串并轉(zhuǎn)換的時(shí)鐘同發(fā)送器一樣處理,收發(fā)設(shè)備間的時(shí) 鐘是會(huì)累計(jì)的,會(huì)導(dǎo)致接收數(shù)據(jù)不正確,波特率控制器就是專門產(chǎn)生一個(gè)遠(yuǎn)遠(yuǎn)高于波特率的 本地時(shí)鐘信號(hào)對(duì)輸入RXD 不斷采樣,以不斷地讓接收器與發(fā)送器保持同步。

波特率控制器實(shí)際上就是一個(gè)簡(jiǎn)單的分頻器。可以根據(jù)給定的系統(tǒng)時(shí)鐘頻率(晶振時(shí) 鐘)和要求的波特率算出波特率分頻因子。已算出的波特率分頻因子作為分頻器的分頻數(shù)。 對(duì)于波特率發(fā)生器中的系數(shù)一般在FPGA 實(shí)現(xiàn)時(shí)往往是固定的,但對(duì)于不同的實(shí)現(xiàn),這個(gè) 系數(shù)需要更改。波特率控制器產(chǎn)生的分頻時(shí)鐘,不是波特率時(shí)鐘,而是波特率時(shí)鐘的16 倍,目的是為了在接收事實(shí)進(jìn)行精確地采樣,以提出異步的串行數(shù)據(jù)。

UART 發(fā)送器由16 個(gè)字節(jié)FIFO 和信號(hào)發(fā)送器組成。FIFO 主要是起到數(shù)據(jù)緩存的作用, 信號(hào)發(fā)送器的核心部分由有限狀態(tài)機(jī)實(shí)現(xiàn)的,實(shí)現(xiàn)偽代碼如下:

case (狀態(tài)機(jī)狀態(tài))

空閑狀態(tài):if ( FIFO 中有數(shù)據(jù) )

狀態(tài)機(jī)跳轉(zhuǎn)到 FIFO 讀取狀態(tài);

else

狀態(tài)機(jī)保持空閑狀態(tài);

FIFO 讀取狀態(tài):讀取FIFO 數(shù)據(jù),保存到移位寄存器;狀態(tài)機(jī)跳轉(zhuǎn)到開始位狀態(tài);

開始位狀態(tài):時(shí)鐘計(jì)數(shù),發(fā)送開始位;計(jì)數(shù)結(jié)束后狀態(tài)機(jī)跳轉(zhuǎn)到數(shù)據(jù)位狀態(tài);

數(shù)據(jù)位狀態(tài):時(shí)鐘計(jì)數(shù),發(fā)送數(shù)據(jù),移位寄存器移位;計(jì)數(shù)結(jié)束后

if(移位寄存器內(nèi)數(shù)據(jù)發(fā)送完畢)

狀態(tài)機(jī)跳轉(zhuǎn)到停止位狀態(tài);

else

狀態(tài)機(jī)跳轉(zhuǎn)到數(shù)據(jù)位狀態(tài);

停止位狀態(tài):時(shí)鐘計(jì)數(shù),發(fā)送停止位;計(jì)數(shù)結(jié)束后狀態(tài)機(jī)跳轉(zhuǎn)到 s_idle;

default:狀態(tài)機(jī)復(fù)位到空閑狀態(tài);

endcase

UART 接收器包括了16 個(gè)字節(jié)FIFO、信號(hào)同步器和信號(hào)接收器三個(gè)部分。其中信號(hào)同 步器則是為了解決串行數(shù)據(jù)幀和接收時(shí)鐘是異步問(wèn)題,其它兩部分和UART 發(fā)送器的中的 功能相似,只是數(shù)據(jù)傳送的方向相反。

3 設(shè)備接口和驅(qū)動(dòng)設(shè)計(jì)

3.1 設(shè)備接口設(shè)計(jì)

AT91ARM9200 芯片通過(guò)其靜態(tài)存儲(chǔ)控制器 (SMC)控制EP1K,而靜態(tài)存儲(chǔ)控制器 (SMC) 是控制外部靜態(tài)存儲(chǔ)器或外設(shè)的訪問(wèn)。 SMC 可編程地址達(dá)512M 字節(jié)。它有8 個(gè) 片選及一個(gè)26 位地址總線。16 位數(shù)據(jù)總線能配置與8 位或16 位外部器件連接。獨(dú)立的讀寫控制信號(hào)允許存儲(chǔ)器與外設(shè)直接連接。SMC 支持不同的允許單時(shí)鐘周期存儲(chǔ)器訪問(wèn)的訪 問(wèn)協(xié)議。它還提供外部等待請(qǐng)求能力。

因?yàn)?EP1K 內(nèi)部設(shè)計(jì)使用的是8 位數(shù)據(jù)總線和8 位地址總線,所以AT91ARM9200 芯片與EP1K 相連的I/O 端口為 A[7:0],D[7:0],NRD 和NWR0。然而EP1K 內(nèi)部采用 的WISHBONE 總線規(guī)范,其讀寫信號(hào)wb_we_o,高電平表示為寫操作,低電平表示為 讀操作。所以需要將NRD 和NWR0 進(jìn)行相應(yīng)的信號(hào)轉(zhuǎn)換。而D[7:0]為雙向端口IO, 所以在EP1K 的設(shè)計(jì)中采用三態(tài)門的設(shè)計(jì)。

評(píng)論