基于FPGA的DDS基本信號發生器的設計

由以上代碼生成的.mif文件即可存E盤目錄下找到,將.mif文件加載到ROM中,實現對ROM的初始化。

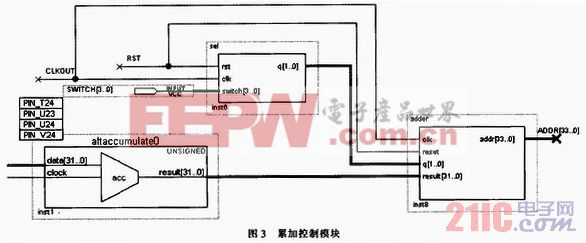

3.2 累加控制模塊

累加控制模塊如圖3所示,為了實現波形選擇性輸出,本設計在累加控制部分增加了選擇器,即圖3的sel模塊,作為系統尋址地址的高兩位,實現對波形查找表的范圍選擇功能。累加器Altaccumulate0的輸出做為累加控制模塊的低32位的輸出,實現在指定范圍內對查找表進行尋址。此設計方法相當于做了一個多路數據選擇器。四位撥扭開關作為sel模塊的輸入控制,將尋址地址轉換成所需波形首地址,即可實現對波形選擇的控制。Adder模塊將sel和Altaccumulate0模塊輸出進行位拼接運算。其部分代碼如下:

always@(posedge clk)

begin

addr={q,32’b0}+{2’b0,result};

end

設計中為了節省ROM的容量而采用相位截斷的方法,取累加器輸出的高十位作為ROM的尋址地址來進行查表。本文引用地址:http://www.104case.com/article/189967.htm

評論