基于FPGA的高精度時間數字轉換電路設計

基于 FPGA的 TDC電路原理如圖 2所示,該電路包括 16位環形移位寄存器 (Ring Shift Register)、16位輸入 4位輸出的編碼電路 (Encoder)、時鐘管理模塊(Clockmgr)、8位通用計數器單元(Counter)、復位邏輯(Reset Logic)和輸出邏輯部分(Out Logic)。其中環型移位寄存器和編碼器組成該電路的細計數器部分,用來控制電路測量精度;通用計數器作為粗計數部分,決定電路的時間測量范圍;時鐘管理模塊通過調用 FPGA內部 PLL資源用來為移位寄存器提供合適的工作時鐘;復位邏輯控制整個 TDC電路的復位動作;輸出邏輯將轉換數字量的細計數和粗計數部分組合為昀終系統輸出。

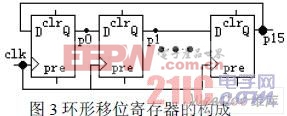

16位移位寄存器構成如圖 3,由 16個帶異步復位和置位端的 D觸發器組成,初始狀態或復位后電路節點 p15被置位高電平,其他節點(p14至 p0)被復位至低電平;正常工作時,在移位脈沖 clk上升沿時高電平在 16個電路節點中循環出現,通過檢查某時刻電路節點的狀態(高電平的位置)可以判斷系統所經歷的移位脈沖 clk的數量,電路的時間分辨率即為 clk的時鐘周期。編碼器對移位寄存器節點狀態編碼并作為測量電路細計數部分的 4位輸出。通用計數器工作在移位寄存器節點 p15的上升沿,其計數周期為移位脈沖周期的 16倍,完成低位到高位的進位計數,并作為測量電路的粗計數部分的 8位輸出。復位邏輯負責環形移位寄存器和通用計數器的復位操作。輸出邏輯分別將粗計數和細計數輸出的 8位和 4位數據組合為測量電路的昀終輸出,并完成數據的校驗。

基于 FPGA的單計數器脈寬測量電路采用在脈沖寬度對應的時間內記數的方法,因高頻工作時計數器會出現跳碼或漏計現象,造成系統錯誤輸出,所以分辨率很難提高 [7]。與單計數器脈寬測量電路相比采用結構簡單的細計數電路能大大提高電路的時間分辨率,并避免了通用計數器極限工作頻率下的跳碼現象,且細計數電路占用極少的片上資源。

3系統實現及優化

Altera公司提供的 Stratix和 Cyclone系列 FPGA芯片具有嵌入式鎖相環( PLL)模塊,該模塊可對外部時鐘進行倍頻分頻及相移操作,可編程占空比和外部時鐘輸出,進行系統級的時鐘管理和偏移控制,常用于同步內部器件時鐘和外部時鐘,使內部工作的時鐘頻率比外部時鐘更高,時鐘延遲和時鐘偏移昀小,減小或調整時鐘到輸出(TCO)和建立(TSU)時間,從而提供完整的時鐘管理方案。使用 Altera Quartus? II軟件無需任何外部器件,就可以調用芯片內部的 PLL來實現相應功能。

該系統時鐘管理模塊調用 FPGA內部 PLL實現,通過 QuartusII設置參數為:Ratio為倍頻/分頻因子(Ratio)為 4,輸出時鐘相移 (Ph) 為 0,輸出時鐘占空比 (DC)為 50%。

該 TDC電路的時間分辨率取決于環形移位寄存器和編碼電路組成的細計數部分,要得到正確的測量數據必須保證對移位寄存器輸出狀態的正確編碼。與 ASIC設計不同,設計者很難預料 EDA軟件布局布線(Layout)后的情況,而且各種不同結構和性能的可編程器件布局布線的結果也不盡相同,而且構成移位寄存器的 D觸發器的時鐘到輸出時間(TCO)和 D觸發器輸入在金屬連線上穩定建立的時間(TSU)也存在一定離散性,使得高頻移位脈沖(納秒級)工作下的移位寄存器在狀態轉換時出現毛刺現象,影響編碼正確輸出,同時編碼器的固有延時特性也限制系統的時間分辨率。該脈寬測量電路系統采用的優化的編碼算法,使得高頻移位狀態下編碼輸出能準確反映環形移位寄存器上各節點狀態,從而保證了該系統的測量精度;移位時鐘為 333MHz(周期 3ns)時在 Altera公司 Stratix和 Cyclone系列芯片上實現了編碼器的正常工作。

該系統包含了粗記數和細記數兩部分電路,粗記數電路在細記數字電路高位輸出(圖 3中 p15)的上升沿工作。但是由于粗記數電路的延時在被測脈沖( clks)上升沿時可能會造成對輸出數據的誤讀。

為解決誤讀現象,在輸出邏輯模塊里加入糾錯電路。對被測脈沖 clks延時 clk周期后產生新時鐘 clks1,在 clks和 clks1的上升沿同時對 q1和 q0取樣并對取樣數據進行處理后作為昀終數據輸出,從而有效地解決了誤讀現象。

移位脈沖工作頻率即為該測量電路的時間分辨率,通過時鐘管理單元可采用不高的外部時鐘便可得到很高的測量精度。

3仿真結果和測試數據

為測試該系統的時間分辨率,為基本時間數字轉換電路附加特定功能電路,使其具有連續測量時鐘脈沖寬度的功能,測試對象是 clks的高電平延續時間。通過改變時鐘脈沖源的頻率來記錄該電路對應的測量數據,從而得到該 TDC電路的時間分辨率。

本文以 QuartusII Web Edition 4.2為軟件平臺,實驗表明,本 TDC設計在 Altera各主流芯品上的時序仿真均能順利通過。適配 Cyclone EP1C3Q240C8芯片的時序仿真表明,移位時鐘為 333M(即分辨率為 3ns),所得到的測試數據輸出正確地反映了被測脈沖的寬度,被測脈沖下降沿到測量數據建立的延時為 5ns。

評論