一種基于Flash型FPGA的高可靠系統設計

本文設計中采用的改進型 TMR,實質上是一種 3+n模冗余,N個子系統中昀多只有三個子系統同時處于運行狀態,其余的 N-3個子系統作為備份隊列,當某個子系統出現錯誤時,表決模塊用備份的子系統替換下錯誤的子系統,繼續維持 TMR結構。當已無備份可用時, 3模冗余系統可以進行降級重構,由 3模冗余降級為 1模。由于延長了三模冗余系統的工作時間,整個系統的可靠性得到了很大提高。

考慮到資源消耗與可靠性提高的平衡,本文設計中采用了 3+1模結構,也就是 3模冗余, 1模備份。3+1模結構的工作方式為:正常時進行三模冗余表決輸出,出現第 1次永久性故障時表決處理模塊能夠檢測出錯誤,在輸出正常信號的同時用備用子系統替換故障子系統,繼續維持 TMR結構;出現第 2 次永久故障時,表決處理模塊仍然能夠檢測出錯誤,在輸出正常信號的同時切除故障子系統,自動降級為單模工作直至單模子系統完全損壞。這種 3+1模結構借鑒了軟件容錯中的恢復塊技術和動態冗余結構,能夠容忍至少 2個子系統錯誤。由于 APA300實現遙控系統資源余量較大,采用了單片 FPGA片內冗余的方案,進一步簡化了系統的復雜度。

3+1模結構的狀態轉移圖如下, TMR、SMR和 Failure三個狀態分別代表三模冗余、單模工作和系統失效。

在設計中,通過冗余單元的互鎖機制(Inter-Lock, IL)來防止錯誤數據通過冗余單元邊界傳播,為此采用了分區約束的方法進行布局布線設計。分區設計不僅能夠隔離錯誤,而且可以充分利用 APA300的 Spine分布,減少路徑延遲。

在用戶約束文件 GCF文件中作如下約束:

這四條語句把 U1~U4四個子系統分別限制在一個 spine內,除了全局時鐘線和輸入輸出線以外,子系統之間沒有直接的連接,這樣分區布局布線以后就能夠有效地隔離錯誤。

在保證可靠性的同時,3+1模設計昀大程度的保證了輸出的實時性,不需要經過關機等待周期、重發指令周期或者輸出不確定周期,能夠連續輸出正確結果直到系統完全倒向錯誤狀態。為了避免系統重構時過快降級,考慮到很多錯誤是瞬時出現又隨即恢復的軟錯誤,因此設定錯誤出現一定次數(例如 3次)以后才去掉故障模塊。

對于 3+1模結構,可靠性提高的代價是付出了 4倍的資源開銷,另外輸出時間延遲會略有增加,因為關鍵路徑上的表決器增加了判斷、替換的邏輯單元。因此這種結構只適用于資源充裕、系統頻率不高的場合。在空間應用系統中,工作速度往往不是昀重要的,因而 3+1模結構實質上是用速度換面積(可靠性),在資源不足的情況下可以只對關鍵模塊、錯誤敏感率高的模塊進行冗余,以節省資源。

4 系統可靠性分析

假設單機的可靠性為(運行 5年后) , 普通 TMR和本文中改進型 TMR的可靠性分別為。由于 2個以上子系統同時發生錯誤的概率很小,假定同一時刻昀多只有一個子系統發生錯誤。

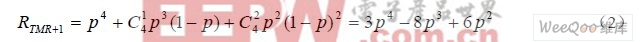

TMR可以容忍 1個子系統錯誤,可靠性相當于 3個子系統都正常的可靠性加上某一個子系統錯誤、其它兩個子系統正常的可靠性:

同理,改進型 TMR的可靠性相當于以下三種情況的可靠性之和:

1)4個子系統都正常

2)1個子系統錯誤,其它 3個子系統正常

3)2個子系統錯誤,其它 2個子系統正常

評論