PowerPCB信號完整性的整體分析與設計

1.3時鐘信號阻抗匹配

本文引用地址:http://www.104case.com/article/189869.htm時鐘信號是各設備工作的基礎,所以時鐘信號的質量尤為重要,在PCB設計時要慎重對待。

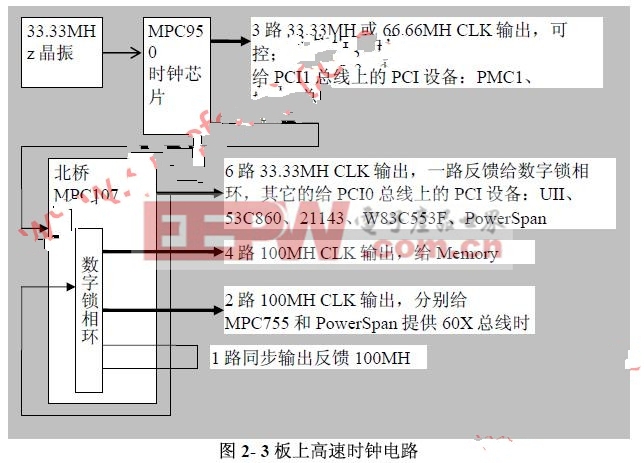

板上時鐘信號很多,主要高速時鐘信號如圖2-3所示。

時鐘芯片的輸出信號阻抗一般都比較小。芯片MPC950的輸出阻抗為7ohm,芯片AV9155的輸出阻抗為10ohm。本板上的時鐘信號都是點對點連接,所以采用串行端接進行阻抗匹配電路設計。

具體串連電阻的大小由HyperLynx仿真后決定。

本板的L2Cache總線工作頻率200Mhz,60x總線工作頻率100MHz,是板上工作頻率最高的部分。依據MPC755、MPC107、PowerSpan的芯片手冊,阻抗在50ohm~70ohm之內比較合適,按前面層疊結構的設計,5mil的信號線寬是可以保證阻抗要求的。

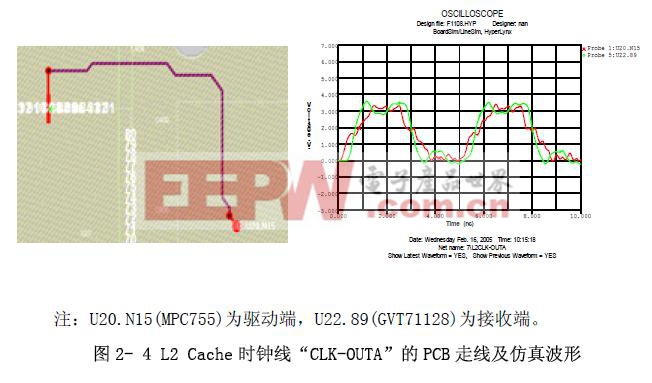

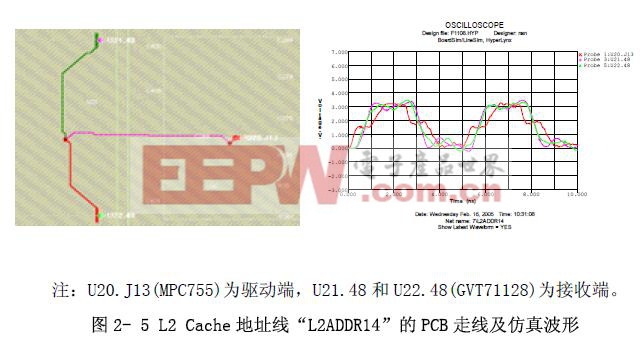

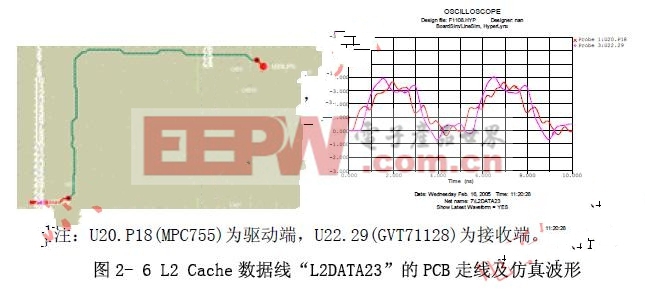

因為板上這兩個總線的負載最多為2個負載,且這幾個芯片之間的距離很近,相關的PCB走線很短,所以信號時序關系一般能夠滿足要求(盡管其工作頻率很高)。下面給出L2Cache總線上典型時鐘線、地址線以及數據線的PCB走線圖以及在HyperLynx仿真軟件的BoardSim工具下的仿真波形。MPC755、MPC107、PowerSpan和GVT71128芯片的IBIS模型均來自于芯片廠商(Motorola、TUNDRA和GALVENTECH)。

評論