基于FPGA的24點離散傅里葉變換結構設計

3 仿真驗證

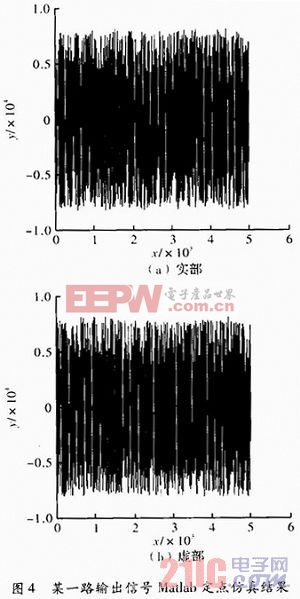

在ISE10.1環境下,采用VHDL完成了24點DFT模塊的開發,并采用Modelsim 6.2 b軟件進行仿真驗證。同時,為驗證設計的24點DFT模塊的正確性,將Modelsim仿真結果與Maltab定點仿真程序結果進行了對比。輸入信號包括24路并行數據信號、1路時鐘信號和1路復位信號,輸出信號包括24路并行數據信號、1路輸出數據有效信號。圖4給出了某一路輸出信號的Matlab定點仿真結果與Modelsim仿真結果對比圖,其中紅色表示Modelsim仿真結果數據,藍色表示Matlab定點仿真結果。從圖4可以看出,該路Modelsim仿真結果與Matlab定點仿真結果一樣。其他路輸出信號Modelsim仿真結果與Matlab定點仿真結果也一樣。從而得出設計的DFT模塊完全正確。該模塊共占用6個Block RAM,14個乘法器,時序仿真結果表明最高工作頻率可達200 MHz,該模塊已經成功應用于某一數字分路項目。

4 結束語

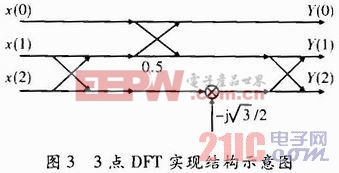

基于Good-Thomas映射算法,并結合ISE10.1軟件提供的FFT IP核,提出了一種易于FPGA實現的24點DFT設計結構,設計的24點DFT模塊主要由3個8點FFT IP核模塊和1個3點DFT模塊構成,并且只需要14個實數乘法器。同時,24點DFT模塊采用流水線結構,最高工作時鐘頻率可達200 MHz。該結構還具有良好的擴展性,只需修改FFT IP核模塊相應的變換點數參數,就可以實現長度為點的DFT。

評論