基于FPGA的UART設計

2.1 波特率發(fā)生器設計

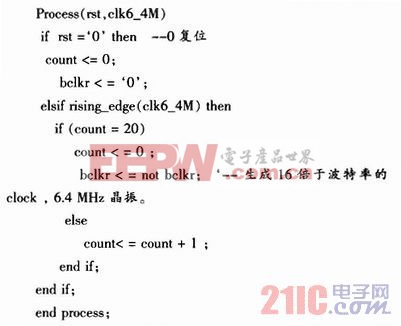

波特率發(fā)生器實質是設計一個分頻器,用于產生和RS232通信同步的時鐘。在系統中用一個計數器來完成這個功能,分頻系數N決定了波特率的數值。該計數器一般工作在一個頻率較高的系統時鐘下,當計數到N/2時將輸出置為高電平,再計數到N/2的數值后將輸出置為低電平,如此反復即可得到占空比50%的波特率時鐘,具體的波特率依賴于所使用的系統時鐘頻率和Ⅳ的大小。如系統時鐘頻率是6.4 MHz,要求波特率是9 600,則16倍波特率時鐘的周期約等于42個系統時鐘周期,則計數器取42/2=21時,當計數溢出時輸出電平取反就可以得到16倍約定波特率的時鐘。

使用VHDL來描述波特率發(fā)生器的完整代碼如下:

2.2 發(fā)送器設計

UART發(fā)送器的設計較容易,只要每隔一個發(fā)送周期按照數據幀格式及要求的速率輸出數據即可。沒有數據要發(fā)送時,發(fā)送數據寄存器為空,發(fā)送器處于空閑狀態(tài);當檢測到發(fā)送數據寄存器滿信號后,發(fā)送器及發(fā)送起始位,同時8個數據位被并行裝入發(fā)送移位寄存器,停止位緊接著數據位指示一幀數據結束。只有發(fā)送數據寄存器為空時,RAM中的待發(fā)數據才能被裝入。程序中使用計數器要保證各位周期定時正確。

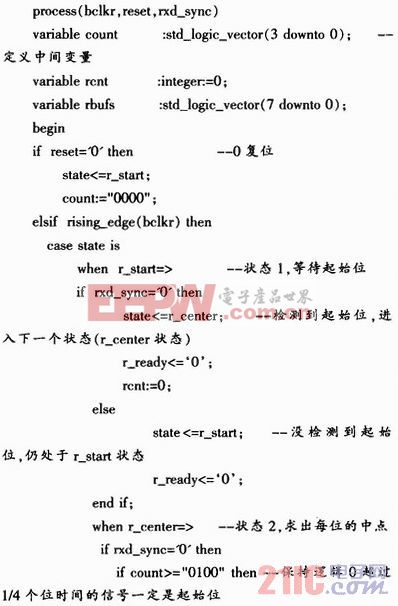

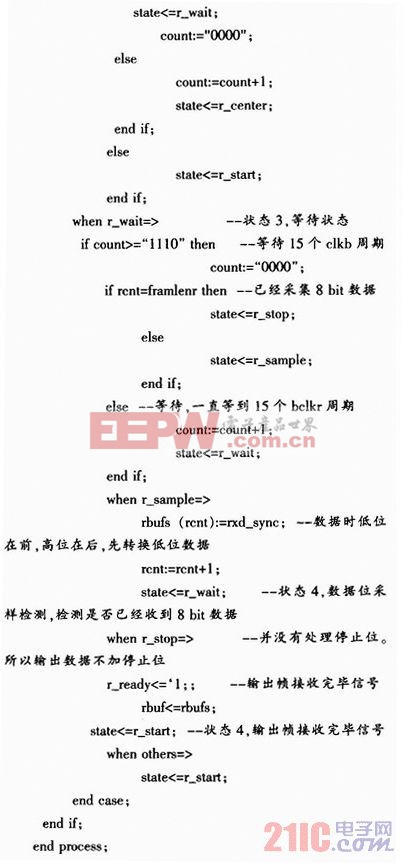

2.3 接收器設計

接收器的工作過程如下,串行數據幀和接收時鐘是異步的,發(fā)送來的數據由邏輯1變?yōu)檫壿?可以視為一個數據幀的開始。接收器先要捕捉起始位,然而,通信線上的噪音也極有可能使傳號“1”跳變到空號“0”。所以接收器以16倍的波特率對這種跳變進行檢測,確定rxd輸入由1到0,邏輯0要8個bclkr(16倍的波特率時鐘)周期,才是正常的起始位,而不是噪音引起的,其中若有一次采樣得到的為高電平則認為起始信號無效,返回初始狀態(tài)重新等待起始信號的到來。

采到正確的起始位后,就開始接收數據,最可靠的接收應該是接收時鐘的出現時刻正好對著數據位的中央。由于在起始位檢測時,已使時鐘對準了位中央,用16倍波特率的時鐘作為接收時鐘,就是為了確保在位寬的中心時間對接收的位序列進行可靠采樣,當采樣計數器計數結束后所有數據位都已經輸入完成。最后對停止位的高電平進行檢測,若正確檢測到高電平,說明本幀的各位正確接收完畢,否則出錯。最

后將正確的數據轉存到數據寄存器中,輸出數據。還要輸出一個數據接收標志信號標志數據接收完。

利用有限狀態(tài)機實現,完整代碼如下:

評論