基于FPGA 的DDR SDRAM控制器在高速數據采集系統中

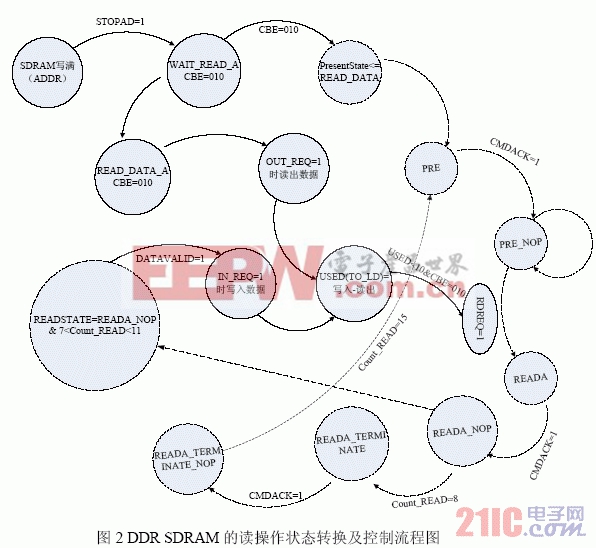

通過對DDR SDRAM 的讀時序的分析,將整個讀操作過程分解為7 個狀態,每一個狀態都對應著不同的命令(CMD)值,DDR 控制核通過對CMD 的譯碼完成對DDR SDRAM的操作。從整體的控制過程來看,讀操作流程如圖2 所示。其中實線表示的是讀操作的控制流程,虛線表示的讀操作的狀態轉換流程。控制流程的實現依賴于控制器內部狀態轉換產生的控制信號。實現各狀態之間切換的控制信號主要有命令應答信號CMDACK,外部控制信號RDREQ 以及程序內部的計數器Count_READ。當系統的主狀態機進入到讀數據狀態時,控制信號CBE=“010”;控制器內部的狀態機進入到讀狀態。讀流程中另一個重要的信號為RDREQ,它是由控制器后端的緩存(FIFO)產生的,當緩存中數據容量低于設定值時,信號RDREQ 被置高,讀狀態由PRE_NOP 進入READA,發起一次讀操作,完成8 個數據的傳送。程序內部的計數器Count_READ 保證控制核在經過設定的CAS 潛伏期后從數據總線上讀取數據。

3 DDR SDRAM 控制器的FPGA實現

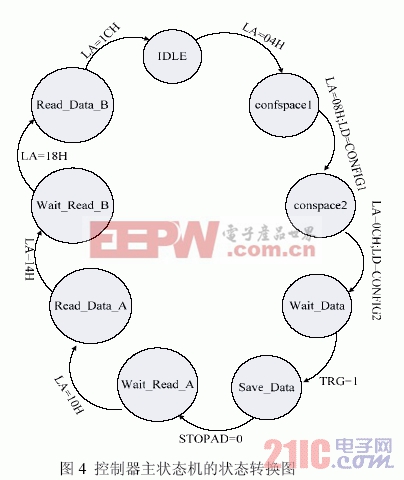

3.1 控制電路主狀態機設計

主狀態機用于控制整個數據采集系統的工作流程。各功能模塊的配合,命令的發送,數據的采集、存儲和傳輸都需要狀態機來協調并嚴格控制時序關系。其狀態轉換圖如圖4 所示。控制器上電或復位時進入IDLE 狀態,其中LA 和LD 分別為PCI 局部總線的地址線和數據線,上位機的發送的命令通過PCI 總線及接口芯片傳送到PCI 局部總線,其中地址線的變化將引起狀態機內部的狀態轉換,狀態轉換的同時,相應的配置字將出現在數據線上。配置完參數之后,轉態機進入等待數據狀態(WAIT_DATA),當觸發信號滿足要求之后(TRG=‘1’),自動進入到保存數據狀態(SAVE_DATA),在此狀態下,控制程序開始進行數據采集。指定存儲深度的數據采集完成后,主狀態機自動進入等待讀數據狀態,在接受到地址線上的狀態轉換命令后,分別進入讀取A 通道和B 通道數據的狀態。數據讀完之后,上位機發送命令使狀態返回到IDLE 狀態。

評論