基于FPGA的多通道頻率檢測技術方案

3.1 延時器的實現

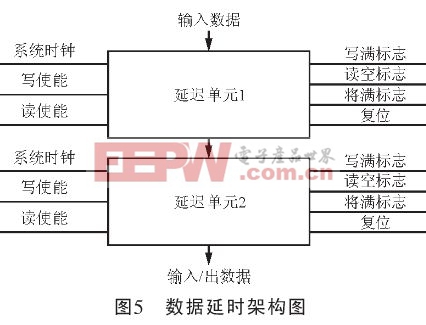

本延時器采用FPGA提供的專用存取模塊FIFO來實現32周期延時,其架構體系如圖5所示。圖中,每個延遲單元即是一個FIFO模塊,FIFO的數據輸出特點為先入先出。在本設計中,第一級延遲器的輸出數據將作為下一個延遲器的輸入數據,就相當于第一級FIFO的數據按先進先出的順序依次向第二級FIFO壓入,相鄰兩級的將滿標志與讀使能信號進行握手協議,從而實現數據的延遲輸出。這樣,設計8個同樣結構的FIFO并進行串行級聯,即可滿足該結構的設計要求。

3.2 系數存儲模塊

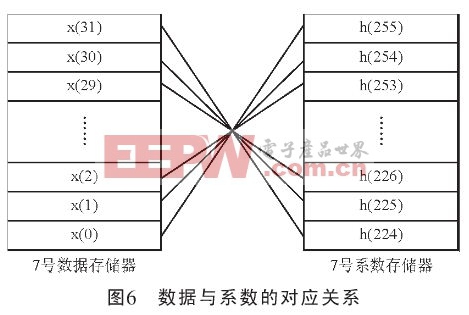

對于256階原型低通濾波器,可以將h(0),h(1),…,h(255)這256個系數分成八組,每組32個,分別存儲到八個存儲器當中,存儲器0存儲的系數為:h(0),h(1),…,h(31);存儲器1存儲的系數為:h(32),h(33),…,h(63);以此類推。存儲器可使用邏輯(LUT)實現,也可使用專用存儲模塊Block RAM來實現。FIFO中的目標數據和存儲器中系數做乘法運算時,兩者的對應關系如圖6所示(以7號存儲器為例)。

當8個數據存儲器的最后一個單元數據被讀出時,8個系數存儲器的0號地址單元的系數也將同時被讀出,然后分別作乘累加,最后作為y(0)輸出。同理,當8個數據存儲器的第二個數據被讀出時,8個系數存儲器的1號地址單元的系數也同時被讀出,然后分別作乘累加,最后的結果作為y(1)輸出,以此類推,得出全部y(2)~y(31)的輸出。最后將y(0)~y(31)作為FFT的輸入數據進行32點FFT運算。

3.3 FFT的實現

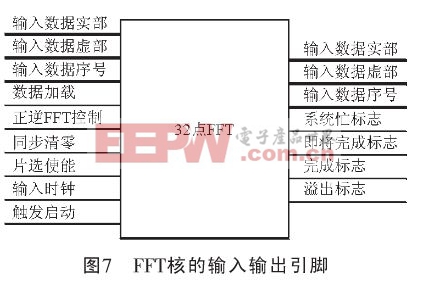

設計中的FFT變換可通過調用Xilinx的IP核來實現。FFT采用流水型結構,該結構能夠對連續數據流進行處理,只是結果上有若干周期的延遲。FFT核的輸入輸出的引腳關系如圖7所示。

3.4 仿真結果

FPGA的設計軟件可采用ALDEC公司的Active_HDL8.2,并可用Testbench文件對所設計模塊進行仿真。Testbench文件讀取時,可由Matlab產生的信號數據作為FPGA仿真的激勵信號,信號形式采用28.1MHz的單頻信號:

將信號數據送入圖4所構建的系統后,即可在ALDEC下得到圖8所示的仿真波形。

由圖8可以看到,該仿真結果在第3號通道上有信號輸出,這與圖3中用Matlab仿真的結果一致,從而驗證該模塊設計的正確性。

4 結束語

本文針對多信道頻率檢測技術進行了研究,并在傳統檢測方法的基礎上,結合FPGA的特點,構建了一種基于DFT多相濾波器組信道化的高效結構。該結構可解決頻率截獲概率與頻率分辨力的矛盾,同時也為實現全概率頻率捕獲提供一種參考方案。經過仿真及測試驗證,該方案能滿足檢測指標要求,從而為多信道頻率檢測技術提供一種設計參考。

評論