基于FPGA的多通道頻率檢測技術方案

0 引言

本文引用地址:http://www.104case.com/article/189762.htm在數字接收機的各種參數中,頻率是最重要的參數之一,它能反映接收機的功能和用途、以及頻譜寬度等重要指標。傳統的順序測頻技術一般通過對接收機頻帶的掃描,對頻域進行連續取樣。該方法原理簡單,技術成熟,但是,其頻率截獲概率與分辨力的矛盾難以解決,無法實現全概率信號截獲。而多信道化的頻率檢測技術屬于瞬時測頻,其架構是采用多個頻率窗口(多個信道彼此銜接相鄰)來覆蓋接收機的整個頻段,這樣,當信號進入任一個窗口時,該窗口的頻率值即可被檢測出。因此,該方法可解決頻率截獲概率與頻率分辨力的矛盾,同時也為實現全概率頻率捕獲提供了一種參考方案。

1 多信道模型

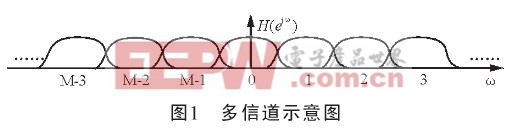

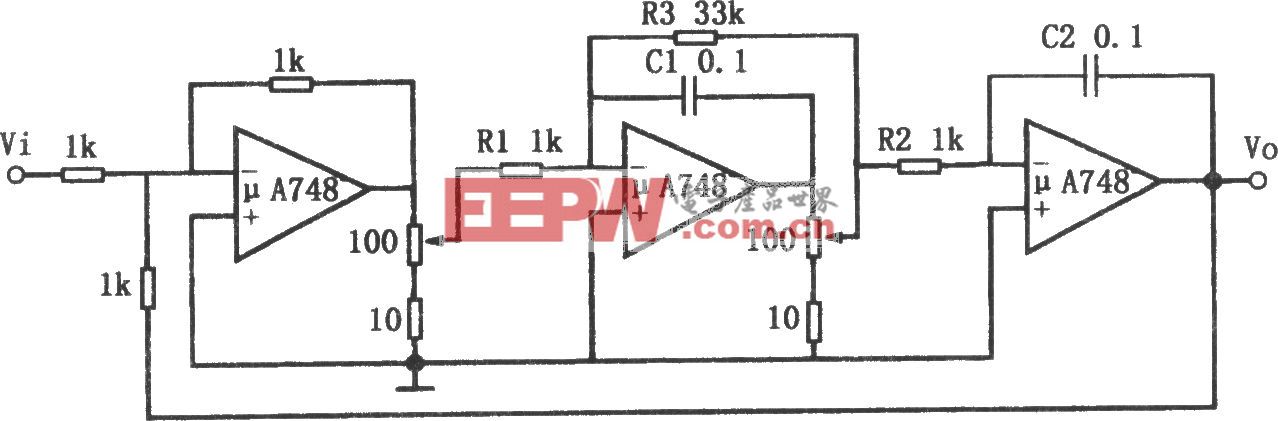

當一個實信號經過A/D采樣之后,再進行正交下變頻處理,即可得到I、Q兩路相位正交信號,它們所構成的是一個復信號。該復信號的信道化示意圖如圖1所示。

圖1所示的信道是一種相互交疊的信道,它們涵蓋了整個零中頻信號的頻率范圍。一般情況下,多信道往往采用數字濾波器組來實現,但該方法需要設計M(M為信道數)個中心頻率不同,而其它性質完全相同的帶通濾波器。這種結構設計過于復雜,同時還加大了后續信號處理的運算速度,對實時處理極為不利。而數字濾波器組的低通型實現方法則是先將每個通道乘以一變換因子,就相當于將實際信號搬移到零中頻,然后再通過LPF得到該頻率信號。該方法可對帶通信號的頻段進行信道化分離,但是帶來的新問題是當LPF用FIR濾波器實現M個濾波運算時,將占用較大的硬件資源,而且系統工作效率較低。目前,該結構已被高效DFT多相濾波器組結構所代替。

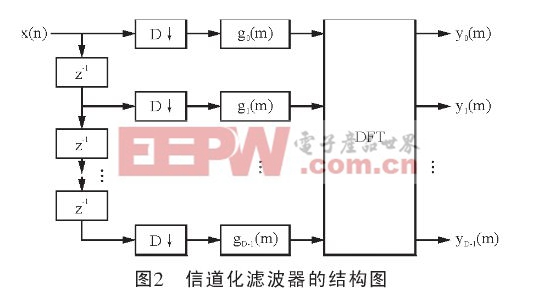

圖2所示是一種具有普遍性的基于DFT多相濾波器組的信道化高效結構,從圖2中可以看出,在濾波之前,先對數據進行D倍抽取可降低濾波過程的運算量,gn(m)是低通原型濾波器hLP(n)的多相分量,其階數可減小到原來的1/D,因而DFT可以用FFT實現。事實上,在此結構中,系統的復雜度和數據速率大大降低,實時處理能力得到了提高。

2 濾波器的設計及仿真

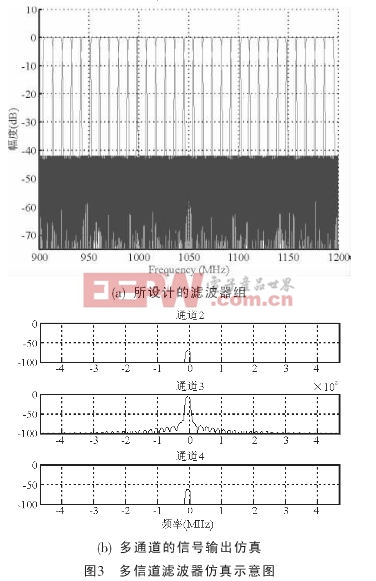

低通型濾波器結構中的每個通道都是由原型低通濾波器乘以旋轉因子形成的。根據要求,圖3所示是由256階原型低通濾波器形成的濾波器組及其信號輸出仿真波形。該信號的有效帶寬為300MHz,共分為32通道,每通道帶寬為9.375MHz.如給此濾波器組送入頻率?=28.1MHz的單頻信號,那么,通過理論計算可知,信號應在第3號通道有輸出。圖3 (b)所示就是第2、3、4通道的輸出仿真結果,可以看出,僅第3個通道有比較強的信號輸出,這與理論上的計算結果是一致的。

3 實現方案

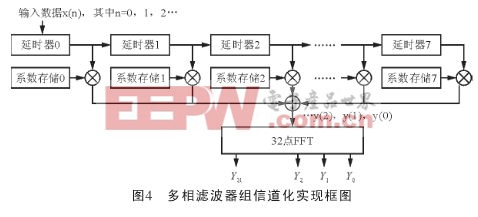

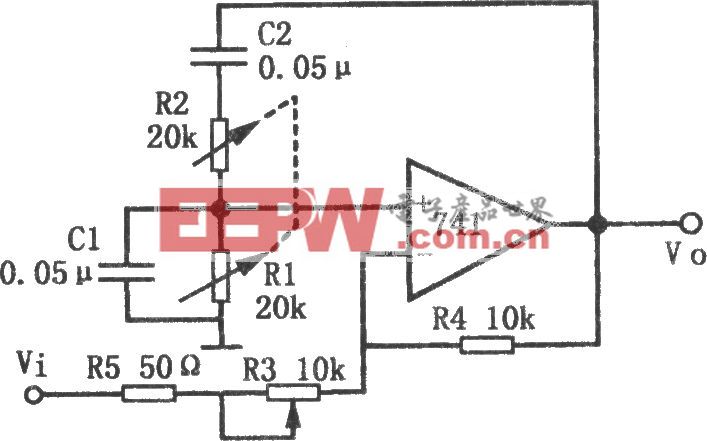

本設計選用的FPGA芯片是Xilinx公司的Virtex-4SX55,該芯片時鐘資源豐富,算術運算單元和專用存儲模塊以及可配置邏輯的使用都很靈活,非常適合當前信號處理系統的功能實現。因此,根據圖2所示的結構,就可以得到一種基于DFT多相濾波器組的信道化解決方案,其具體實現結構如圖4所示。

圖4所示結構由延時器、系數存儲器、乘加器和FFT組成。其中延遲器可實現對輸入數據32個周期的延時,存儲器用于存儲濾波器系數。下面對該結構中幾個主要組成模塊的實現及仿真結果進行介紹。

評論