基于消息機制的片上多處理器系統的研究

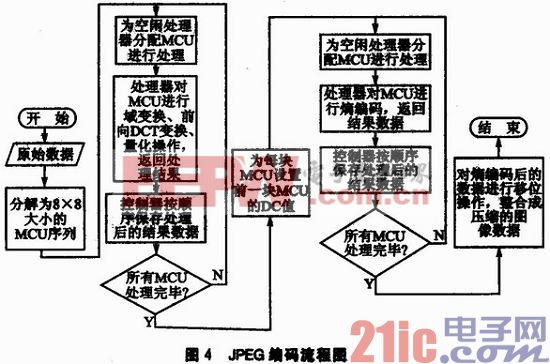

由上述公式可見,前向DCT變換是相當耗時的一部分,因為該部分需要求取余弦值,然后求積與求和,并且進行的都是浮點運算;運用快速算法可減少該部分的處理時間。在JPEG編碼框圖中,前向DCT處理的都是8×8大小的數據塊,每個數據塊之間相互獨立,因此可同時進行計算。在熵編碼過程中,對直流系數DC的編碼采用的是差分脈沖編碼調制(DPCM)方法,需要用到前一塊MCU數據的DC值,所以需要等待前一塊MCU的量化結果,結合本文所設計的系統,采用1:1:1的壓縮比,可將JPEG編碼算法按圖4所示的流程進行分解處理。本文引用地址:http://www.104case.com/article/189737.htm

在Altera公司的芯片EP3C25F324C8上利用SOPC完成了圖1所示的系統體系結構。用Quartus軟件進行綜合,綜合結果如表1所列。利用Nios II IDE完成了JPEG編碼程序。程序運行時,利用時間戳(timestamp)測得圖像編碼所用的時間,并用公式Sp==T1/Tp計算得到加速比Sp,其中T1是單處理器時的運行時間,Tp為有p個處理器時的運行時間。結果如表2所列。

在FPGA中,LE的開銷量Z可分為處理器用量X與系統用量Y,因此Z≈N×X+Y,結合表1的數據可計算得出,一個處理器對應的LE使用量約為3 769,占總量的15.3%。

在表2中,PC機的處理頻率是FPGA軟處理器的頻率的2 000/100=20倍,FPGA單處理器的處理時間是PC機的5 601 730/20 861≈268倍,可見與頻率不成正比。主要原因為PC機支持浮點運算,而FPGA的軟核處理器為定點運算。

由表2可看出,每增加一個處理器,加速比可提升50%,因此增加處理器的數量可明顯提升系統性能,而增加一個處理器在硬件上只需增加15.3%的開銷,因而具有一定的性價比。另外,由于處理器之間是相互獨立的,并在硬件結構與軟件設計上保持一致,這使得當增加處理器時,只需修改一些配置參數即可,這有利于減少增加處理時的工作量和開發成本。

系統運行于4個處理器時,運行過程中突然斷開一個處理器,模擬處理器出現問題的情況,測得系統仍能正常輸出,運行時間為2 551 542 μs。相比正常情況的2 108 085μs,顯然處理時間有所延長,但此時系統仍能正常輸出,因而證實了該系統具有一定的容錯性。

結語

針對目前多處理器系統針對性強、開發難度大、不具備容錯性的不足,本文提出了一種基于消息機制的多處理器系統,實現了多處理器系統的通用性設計,簡化系統的設計難度,同時具有一定的容錯性與穩定性。在文中利用FPGA技術進行仿真驗證。系統實驗表明,增加處理器數量可明顯提升系統的性能,并具有一定的性價比。在系統中的某一個處理器出現問題時,系統仍能正常輸出,具有一定的容錯性。

評論