FPGA的寬帶步進頻率信號源設計

通過RS公司FSP頻譜分析儀,分別對單頻和步進頻率進行實際測試。單頻點測試通過FPGA編程配置射頻輸出功率為+1 dBm,測試輸出功率與相位噪聲,測試結果如表1所列。本文引用地址:http://www.104case.com/article/189736.htm

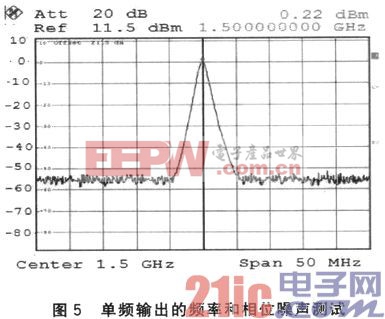

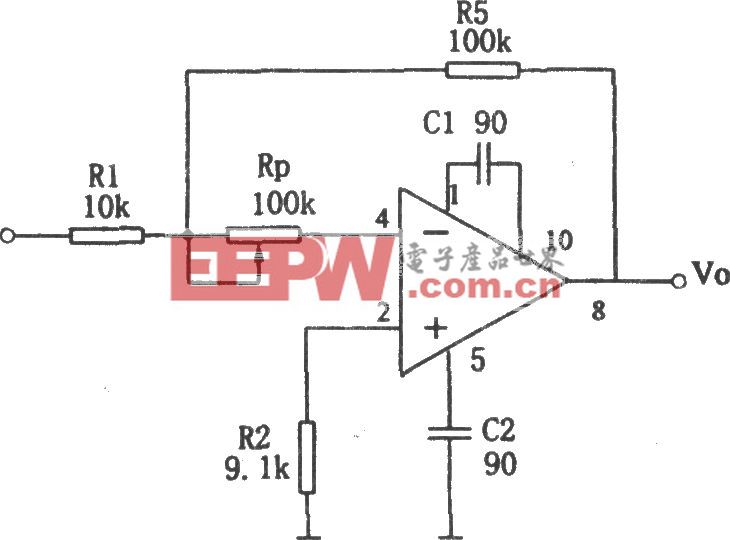

測頻單點頻率輸出為1.5 GHz,頻譜分析儀的SPAN寬度為50 MHz,輸出功率為0.22 dBm,相位噪聲為-93.83 dBc@10kHz,測試結果如圖5所示。

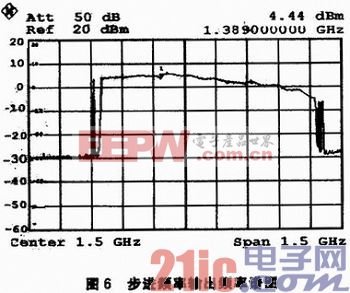

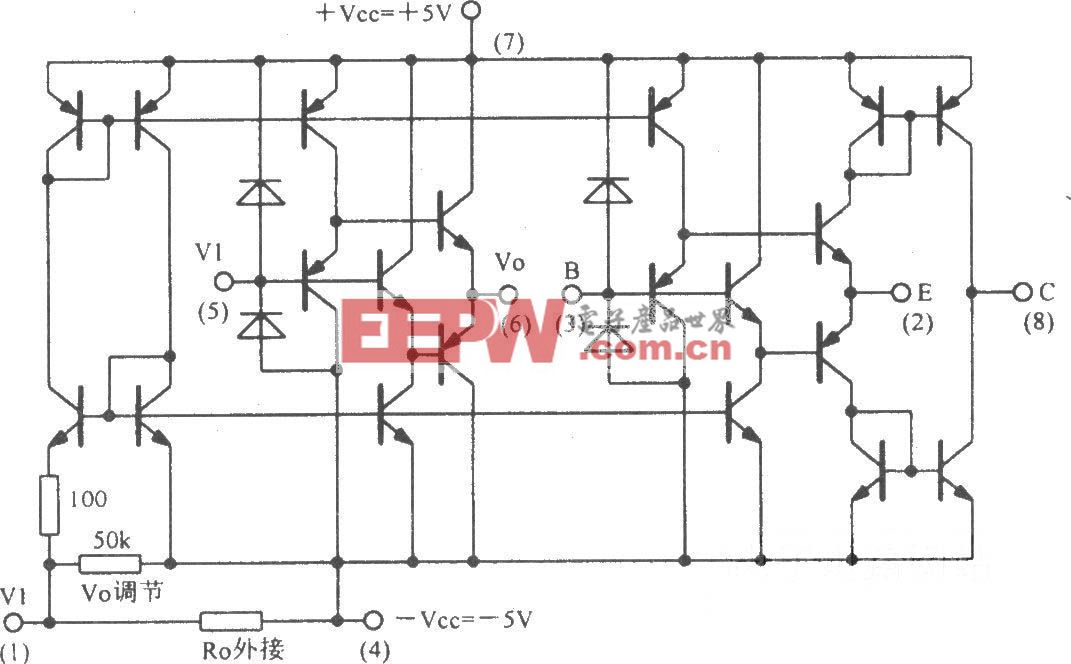

由FPGA配置,設定每個步進頻點的保持時間為100 μs,通過頻譜分析儀,測試寬帶步進頻率的功率值,結果如圖6所示。

根據測試結果,本方案設計各項指標基本滿足設計要求。由于傳輸線的衰減和反射作用,導致步進頻率掃描輸出功率不夠平穩。本文設計的寬帶步進頻率源的后級可通過擴展數控衰減器、放大器、選頻濾波器等網絡,將有利于調整輸出功率的平穩度和帶外雜散抑制。

結語

本方法設計的LS波段寬帶步進頻率信號源結合了DDS和鎖相環芯片二者的優點,在FPGA的綜合配置、控制下完成了滿足要求的頻率源設計要求。如果將VCO的基準電壓更新頻率按其16重疊頻段設置,即整個頻率輸出僅更新16次基準電壓,那么在單個VCO線性區間,輸出頻率的穩定時間將為納秒級,該方法將在后期的設計中重點研究。采用本方法設計的寬帶步進頻率源具有集成度高、頻率穩定性能好、電路簡單、低功耗等特點。同時,該頻率源作為通用電子設備頻率源,可通過FPGA配置輸出135 MHz~4.4 GHz的帶寬輸出,具有廣泛的工程實用價值。

fpga相關文章:fpga是什么

分頻器相關文章:分頻器原理 電荷放大器相關文章:電荷放大器原理 鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理

評論