基于OpenBus系統(tǒng)的FPGA嵌入式設(shè)計(jì)與實(shí)現(xiàn)

摘要:隨著FPGA技術(shù)的發(fā)展,FPGA設(shè)計(jì)已不再只是硬件電路的設(shè)計(jì),而是包含處理器、外國組件和接口邏輯在內(nèi)的完整數(shù)字系統(tǒng),同時在處理器中編程完成嵌入式代碼的FPGA“軟”設(shè)計(jì)。與傳統(tǒng)的主要基于硬件描述語言進(jìn)行FPGA設(shè)計(jì)井發(fā)不同,本文在電路設(shè)計(jì)軟件Altium Desi gner開發(fā)環(huán)境下,結(jié)合Xilinx公司的ISE設(shè)計(jì)軟件,在Altium Designer的創(chuàng)新電子設(shè)計(jì)平臺NanoBoard 3000上,設(shè)計(jì)實(shí)現(xiàn)了基于Altium Designer特有的系統(tǒng)級設(shè)計(jì)方法OpenBus系統(tǒng)的32位處理器控制LED的FPGA嵌入式設(shè)計(jì)。

關(guān)鍵詞:FPGA嵌入式設(shè)計(jì);Altium Designer軟件;OpenBus系統(tǒng);NanoBoard 3000

現(xiàn)場可編程門陣列FPGA(Field Programmable Gate Array)是美國Xilinx公司于1984年首先開發(fā)的一種通用型用戶可編程器件。FPGA內(nèi)部由可綰程邏輯單元陣列、布線資源和可編程的I/O單元陣列構(gòu)成,包含豐富的邏輯門、寄存器和I/O資源。目前,面向大規(guī)模可編程器件附的廣泛應(yīng)用,正在不斷地加速電子設(shè)計(jì)技術(shù)從硬件電路設(shè)計(jì)向“軟”設(shè)計(jì)的過渡。Altium Designer是傳統(tǒng)電路設(shè)計(jì)軟件Protel的高端設(shè)計(jì)版本,除了具備基本的電路原理圖設(shè)計(jì)和PCB設(shè)計(jì)功能外,它的特色主要在于增強(qiáng)了FPGA開發(fā)功能,將電子產(chǎn)品的板級設(shè)計(jì)、可縮程邏輯設(shè)計(jì)和嵌入式設(shè)計(jì)開發(fā)融合在一起。

傳統(tǒng)的FPGA系統(tǒng)設(shè)計(jì)多是基于硬件描述語言VHDL或者Verilog來完成的,需要開發(fā)者具備一定的硬件描述語言知識,而且這種方式的設(shè)計(jì)就可讀性而言具有一定的復(fù)雜度。Altium Designer提出了一種系統(tǒng)級的設(shè)計(jì)概念——OpenBus系統(tǒng),這是一種全新的系統(tǒng)級的FPGA設(shè)計(jì)方法。這種設(shè)計(jì)方法避開了傳統(tǒng)的FPGA設(shè)計(jì)中用硬件描述語言來編程、仿真和驗(yàn)證等步驟,以更加抽象的方式表示了處理器與外圍設(shè)備間的互聯(lián),降低了FPGA設(shè)計(jì)的復(fù)雜度,簡化了FPGA設(shè)計(jì)。

Altium Designer的創(chuàng)新電子設(shè)計(jì)平臺NanoBoard 3000提供了將嵌入式智能作為設(shè)計(jì)核心的設(shè)計(jì)環(huán)境,在這個平臺上可以調(diào)試、下載FPGA嵌入式設(shè)計(jì),實(shí)現(xiàn)電路硬件設(shè)計(jì)和基于“軟核”處理器的嵌入式軟件設(shè)計(jì)。

1 基于OpenBus系統(tǒng)的設(shè)計(jì)要素

1.1 OpenBus瞄系統(tǒng)

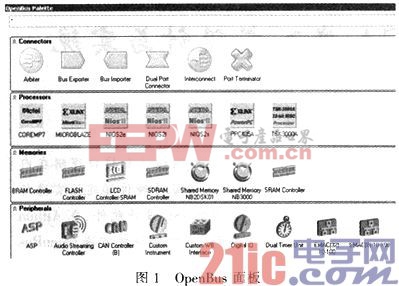

“OpenBus系統(tǒng)”是一個描述一種使用普通總線實(shí)現(xiàn)整個系統(tǒng)內(nèi)邏輯功能性“模塊”連接的術(shù)語。通過這種方法,用戶能夠很快地裝配一個包含滿足應(yīng)用需求的各種功能在內(nèi)的系統(tǒng)。具體來說,OpenBus系統(tǒng)是Altium Designer軟件自帶的高端IP模塊,包含Connectors(連接器)、Processors(處理器)、Memories(存儲器)、Peripherals(外圍設(shè)備)等,如圖1的OpenBus Palette面板所示。設(shè)計(jì)時可以根據(jù)設(shè)計(jì)需求,直接在OpenBus Palette面板調(diào)用相關(guān)的IP模塊,即OpenBus器件,連接構(gòu)成設(shè)計(jì)系統(tǒng)。但要注意的是,這些IP模塊在調(diào)用后,還需要進(jìn)行相應(yīng)的參數(shù)配置才能使用。這種OpenBus系統(tǒng)的設(shè)計(jì)方法與傳統(tǒng)的將處理器和外圍電路作為元件放置在電路板上不同,它移除了所有低級別的走線和互連細(xì)節(jié),能夠快速地構(gòu)建系統(tǒng)。

1.2 FPGA設(shè)計(jì)元件庫與軟件平臺搭建器

除了OpenBus Palette面板中的OpenBus器件,要完成FPGA嵌入式設(shè)計(jì),還需要使用Altium Designer軟件中的FPGA設(shè)計(jì)元件庫。這些元件庫提供了FPGA設(shè)計(jì)中所需的外圍器件。Altium Designer軟件提供的常用的FPGA設(shè)計(jì)元件庫有:FPGA NB3000 Port-Plugin.IntLib、FPGA Peripherial.IntLib、FPGA Generic.IntLib、FPGA Configumble Generic.IntLib、FPGA Instruments.IntLib等。

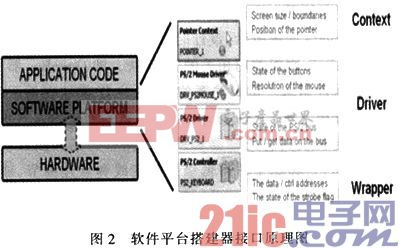

與OpenBus系統(tǒng)配合進(jìn)行FPGA嵌入式設(shè)計(jì)的,還有軟件平臺搭建器SwPlatform。因?yàn)檫M(jìn)行FPGA嵌入式設(shè)計(jì)時,F(xiàn)PGA器件的外圍引腳常需要驅(qū)動如LED、觸摸屏、揚(yáng)聲器等硬件設(shè)備。而要使這些硬件設(shè)備能正常工作,就要在設(shè)計(jì)中包含相應(yīng)的驅(qū)動代碼。這些硬件的驅(qū)動代碼無需自行編寫,Altium Designer的軟件平臺搭建器SwPlatform可以把所有連接外設(shè)所需的低階驅(qū)動代碼整合一起。軟件平臺搭建器SwPlatform采用圖形化方式連接用戶的應(yīng)用程序與底層硬件。在進(jìn)行FPGA設(shè)計(jì)時,軟件平臺搭建器SwPlatform可以自動地由FPGA設(shè)計(jì)的硬件部分獲取底層硬件的信息。如圖2所示,軟件平臺搭建器SwPlatform自動根據(jù)底層信息(Wrapper,棧層中的HARDWARE部分)提供對于硬件的驅(qū)動(Driver,棧層中的SOFTWARE PLATFORM部分)以及服務(wù)程序(Context,棧層中的APPLICATION CODE部分)。設(shè)計(jì)時只需關(guān)注構(gòu)建設(shè)計(jì)本身的應(yīng)用程序代碼,不需要考慮過多的底層驅(qū)動代碼。

評論