TS流的CRC譯碼器設(shè)計(jì)

3.4 接收模塊

接收模塊的主要功能就是檢測(cè)到起始位后再在每個(gè)數(shù)據(jù)的中央位置進(jìn)行采樣,接收完一幀數(shù)據(jù)后就放到接收FIFO里供CRC校驗(yàn)?zāi)K使用,其RTL視圖如圖6所示。本文引用地址:http://www.104case.com/article/189722.htm

4 CRC校驗(yàn)

CRC校驗(yàn)有兩種方法:一種是按位來(lái)計(jì)算的,一種是按字節(jié)來(lái)計(jì)算的。按位來(lái)計(jì)算的占用FPGA邏輯資源比較少,但是相對(duì)來(lái)說(shuō)速度會(huì)比較慢,不能適應(yīng)高速的TS流的要求。按字節(jié)來(lái)運(yùn)算的速度快,但是占用FPGA的邏輯資源多。綜合考慮后,這里使用按字節(jié)的算法。

本設(shè)計(jì)的CRC算法采用直驅(qū)動(dòng)表法,由于一個(gè)字節(jié)只有8 b,與生成項(xiàng)進(jìn)行異或后最多有256個(gè)結(jié)果,先將256個(gè)待查表的值生成MIF文件,放入由FPGA的IP核生成的ROM里,然后用查表法可以達(dá)到很快的運(yùn)算速度,具有很強(qiáng)的實(shí)時(shí)性。其具體算法如下:

crc_reg=crctab[crc_reg[31:24]^buffer[7:0]8'hff]^{crc_reg[23:0],8'h0};

圖7是用model sire對(duì)CRC進(jìn)行仿真的結(jié)果使用的是PSI表里的一個(gè)section的數(shù)據(jù),可以看到,校驗(yàn)到最后的時(shí)候,crc_reg的值變?yōu)榱?,說(shuō)明數(shù)據(jù)是正確的。

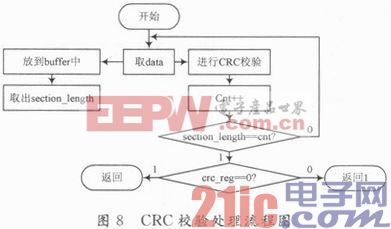

只要在接收FIFO里有數(shù)據(jù),CRC模塊就會(huì)將讀取數(shù)據(jù)進(jìn)行CRC校驗(yàn)。而每個(gè)PSI表里都有一個(gè)section_length是記錄在這個(gè)表里面從該字節(jié)之后有多個(gè)字節(jié)是有效數(shù)據(jù)的。所以,要將這個(gè)數(shù)據(jù)提取出來(lái)再加上3就得到了整個(gè)表的長(zhǎng)度。在CRC校驗(yàn)的時(shí)候,也要設(shè)置一個(gè)計(jì)數(shù)器,用于記錄處理多少個(gè)數(shù)據(jù),并與section_length比較。若這兩個(gè)數(shù)相同,則判斷CRC寄存器里的值;若為0,則說(shuō)明這個(gè)數(shù)據(jù)段是正確的,通過(guò)串口發(fā)0x00給上位機(jī);若CRC寄存器不為0,則說(shuō)明這個(gè)數(shù)據(jù)斷是錯(cuò)誤的,F(xiàn)PGA發(fā)送0x01給上位機(jī)。

CRC校驗(yàn)處理的流程圖如圖8所示。

5 結(jié)論

本系統(tǒng)經(jīng)過(guò)實(shí)際驗(yàn)證具有很高的準(zhǔn)確性和實(shí)時(shí)性,并且在上位機(jī)和FPGA上都進(jìn)行了校驗(yàn),可以驗(yàn)證是否數(shù)據(jù)在串口傳輸?shù)倪^(guò)程發(fā)生了錯(cuò)誤,其FPGA部分可以當(dāng)作一個(gè)獨(dú)立的模塊加入到其他系統(tǒng)中,具有很強(qiáng)的實(shí)時(shí)性。

評(píng)論