基于FPGA的空間電場信號采集系統設計

2.2 數字濾波器的實現

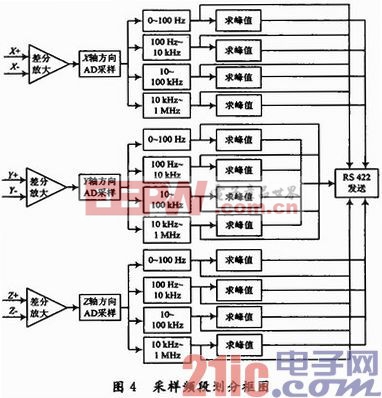

借助Matlab中的濾波器設計和分析工具FDATool,其操作簡單、靈活,用戶只需在GUI中輸入設計需要的濾波器各項參數,就可以獲得需要的數字濾波器。本設計中共劃分為4個頻段:0~100 Hz,100 Hz~10 kHz,10~100 kHz,100 kHz~1 MHz,經實驗發現,頻帶寬度過大的帶通濾波器性能不是很理想,通帶內幅度并不平坦,失真較大。因此除了第一個頻段采用低通濾波器外,另外三個頻段采用低通濾波器+高通濾波器的方法來實現,如頻帶為100 Hz~10 kHz可以用截止頻率為10 kHz的低通濾波器和100 Hz的高通濾波器相加得到。將生成的FIR濾波器系數.coe文件導入4個Xilinx ISE中的IP核中,分別例化生成四個FPGA片內的數字濾波器,對X,Y,Z三個方向采集到的電場信號進行頻段的劃分。

2.3 同步422

將X,Y,Z每個方向的各個通道的濾波后的信號,加上包頭、時間碼、通道號、校驗碼之后通過422芯片DS26LV31AT、發送給后端的設備。主要包括兩個子模塊:波特率產生模塊和發送模塊。

波特率產生模塊:系統外接18.432 MHz晶振,用來產生同步422通信所需要的115 200 b/s的波特率。本模塊采用10 MHz時鐘。波特率的計算:(1/115 200)/(1/1×107)=86個系統時鐘周期,為得到50%占空比的波特率時鐘,使得計數器在計數到86/2=43時將輸出置高,之后在計數到86時將輸出置低并重新計數,就可實現所需波特率的時鐘;發送模塊:采用狀態機進行編寫,由五個狀態(IDLE,WAIT,STAR T,SHIFT,STOP)和一個進程組成。

3 系統實現

本設計系統硬件設計采用Altium Designer 6.0繪制原理圖和PCB圖,FPGA程序設計則是在Xilinx ISE 11和Modelsim SE 6.5e平臺上設計和仿真,濾波器系數則是在Matlab中的FDA tools工具箱中生成并導入ISE中的有限脈沖響應的知識產權核中。本文引用地址:http://www.104case.com/article/189721.htm

在系統的輸入端加入-3~3 V的模擬輸入電壓進行測試,進行FPGA片上數據采集處理實驗,在每個模塊的輸出端添加測試焊點,方便逐步調試。系統設計框圖如圖4所示,根據后端收到的實驗數據對比可知,本系統設計完成了設計要求。

4 結語

本文提出的基于FPGA的空間電場信號采集系統應用于探空火箭有效載荷——箭載電場儀探頭后端信號采集與處理部分,也可以為地面電場儀處理電場信號提供服務。該方案解決了電場信號采集系統設計要求,避免了模擬濾波電路易受溫度、噪聲等影響,硬件電路大大簡化,可調適性好。經過實踐證明本設計方法設計正確,減輕了設計者對于龐大模擬電路的設計負擔,系統運行穩定可靠,可移植性強,可用于多種數據采集電路的設計,有一定的參考價值。

模擬信號相關文章:什么是模擬信號

adc相關文章:adc是什么

fpga相關文章:fpga是什么

評論