基于FPGA的空間電場信號采集系統(tǒng)設計

1.3 電源模塊

該模塊為系統(tǒng)各個模塊提供輸出穩(wěn)定的電源。

FPGA供電電壓分為3部分,每個bank的電壓(VCCO),參考電壓(VCCAUX),內核電壓(VCCINT)。XC3S500E芯片bank電壓為3.3 V,參考電壓為2.5 V,內核電壓為1.2 V。電源模塊選用TI公司的TPS767D325和TPS62003兩款芯片,TPS767D325將供電電壓5 V轉換為3.3 V和2.5 V,提供給FPGA的bank電壓和參考電壓,而TPS62003則將二級電源3.3 V轉換成1.2 V,提供給內核電壓。

1.4 FPGA控制器模塊

FPGA用來控制A/D采樣和同步422發(fā)送,F(xiàn)PGA采用的是Xilinx公司Spartan-3E系列的XC3SS00E芯片,它大約有500 k個門,10 476個等效邏輯單元,73 Kb的分布式RAM,360 Kb的塊RAM,4個數(shù)字時鐘管理單元,232個I/O引腳,92個差分I/O引腳。外圍電路較為簡單,全局時鐘從GCLK引腳進入FPGA,保證了系統(tǒng)的可靠性。

XC3S500E芯片的配置芯片選用XCF04,容量為4 Mb,3.3 V的核電壓,擁有串行配置接口。

2 FPGA程序設計

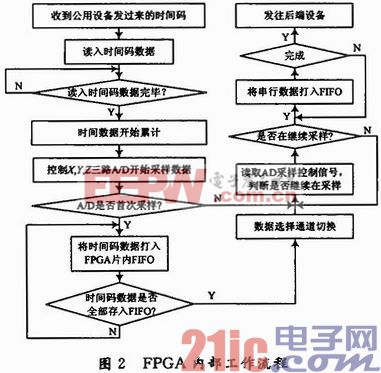

FPGA程序采用Verilog語言編寫,主要分為三部分的代碼:A/D控制程序、例化FIR的IP核產生數(shù)字濾波器、同步422發(fā)送程序。FPGA內部的工作流程圖如圖2所示。本文引用地址:http://www.104case.com/article/189721.htm

2.1 FPGA對AD1610采樣的控制

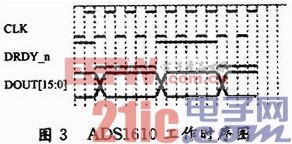

當不使用ADS1610的時候,可以把nPD引腳置低,這樣就關掉了ADS1610的電源,在設計中將nPD引腳置高。ADS1610為并行數(shù)據(jù)傳輸,在數(shù)據(jù)準備就緒之后,需要保持時間來確保上一組數(shù)據(jù)有效,經過建立時間之后開始接收下一組數(shù)據(jù),時序圖如圖3所示。

引腳nSYNC可以用來同步多片.ADS1610,單片設計時為復位引腳,這里設計不采用多片同步,將nSYNC置低時,ADS1610是異步復位的。當復位的時候,所有的數(shù)字電路清零,16位輸出引腳DOUT[15:0]被全部置為低,而數(shù)據(jù)就緒引腳nDRDY被置為高。在程序的設計中,nSYNC在時鐘信號的下降沿拉高,則nDRDY在接下來的第二個時鐘上升沿拉低。

模擬信號相關文章:什么是模擬信號

adc相關文章:adc是什么

fpga相關文章:fpga是什么

評論