利用CPLD實現FPGA的快速加載

這種加載方式的原理是:先將FPGA的配置數據放在CPU外掛非易失性存儲器中,CPU啟動后,CPU通過GPIO模擬時序的方式將配置數據加載到FPGA中。CPU以這種方式產生的加載時鐘只有kHz,加載一個10 MB大小的配置文件大概需要100 s。通過優化代碼可以減小加載時間,但是軟件不能模擬高頻時鐘是其固有的缺陷。CPLD可以利用外部高速時鐘作為加載參考時鐘,且由于它控制簡單,擴展方便的特性,可以作為加載的橋梁,在CPU和FPGA之間建立快速加載的通道。

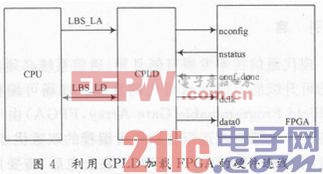

利用CPLD進行PS加載的電路連接設計如見圖4。本文引用地址:http://www.104case.com/article/189703.htm

CPU要從外掛存儲器中讀取配置文件,然后發起加載任務,通知CPLD開始加載并通過Local Bus向CPLD發送加載數據。常用的CPU Local Bus參考時鐘約為66 MHz,加載1 B的數據需要約15璐。CPLD對外部參考時鐘(可選擇,本文選用66 MHz晶振)進行4分頻后作為加載時鐘,此時鐘約為16.5 MHz,其加載效率比CPU GPIO加載方式提高10倍以上。

2.2 CPLD加裁模塊的設計

CPLD加載模塊主要是利用CPLD邏輯代碼實現PS加載時序,達到快速加載的目的。FPGA的PS加載時序如圖5所示。

PS加載的過程如圖6所示。

根據PS加載的時序和流程圖,設計通過CPU和CPLD對FPGA進行加載的過程如下:CPLD在收到CPU發出的加載開始命令后,將nconfig信號拉低(器件時序對nconfig的低電平脈寬有要求),當FPGA收到nconfig的低脈沖有效信號后,會馬上清除現有的程序進入加載狀態,拉低nstatus和conf_done信號,在nconfig信號變高500 μs(器件要求)后CPLD可以開始向FPGA送時鐘和數據進行加載,加載完成后,FPGA將conf_done信號拉高,遞知CPLD,CPLD再通知CPU加載已完成,PPGA進入初始化階段。

要實現成功的加載,必須保證加載過程正確,加載時序滿足器件要求。還要注意與CPU軟件程序的配合。

(1)nconfig信號時序的控制。nconfig信號時序控制由CPU軟件實現,在硬件連接上,將nconfig信號使用外部電阻上拉,軟件對CPLD寄存器中的configbit先寫0,再寫1,中間延遲10μs,保證nconfig信號的脈寬達到芯片要求。

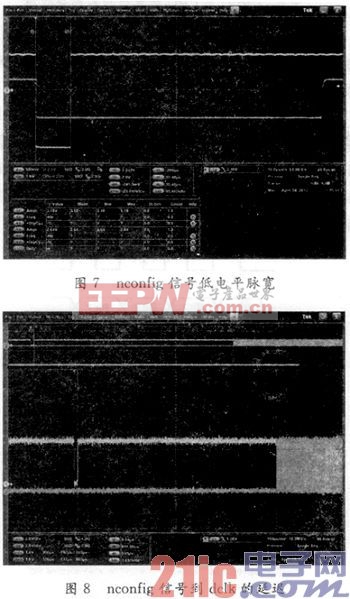

實際測試波形如圖7所示,橫軸表示時間,靠上的信號線為nconfig信號,靠下的為nstatus信號,nconfig脈寬約為11μs,滿足要求。

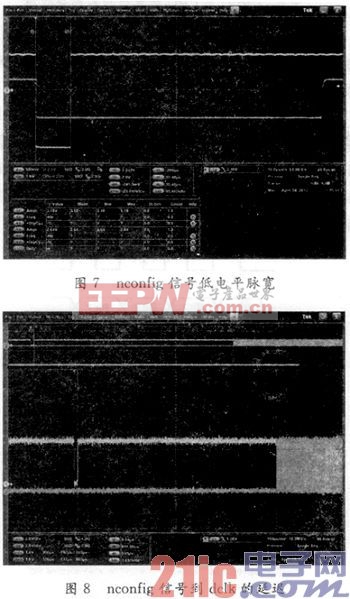

(2)dclk時序的控制。dclk由CPLD的參考時鐘elk_ref四分頻產生。器件要求dclk在nconfig信號變高后至少500 μs后才輸出,這個時序是由CPU軟件來控制,軟件先將nconfig信號拉低10 μs,等待FPGA回應的nstatus,當nstatus高電平到來后,延遲600μs開始通過Local Bus向CPLD發送數據,同時置位時鐘使能標志位,CPLD以此時鐘標志位來觸發dclk,以此保證dclk的時序。實際測試波形如圖8所示。橫軸表示時間,靠上的信號線為nconfig,靠下的為dclk,從nconfig變高到dclk輸出的延遲約為605μs,滿足要求。

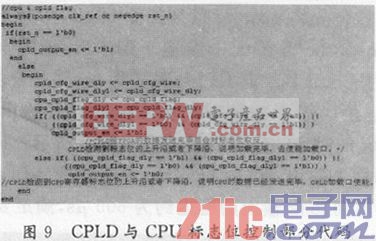

(3)CPLD與CPU標志位的控制實現。必須控制CPLD加載口在CPU送數據完成之后再工作,否則會引起數據阻塞。為了實現這一控制,CPU會送出一個標志位,即CPU在第一個Local Bus的訪問周期發送8 b加載數據,在下一個周期CPU會對標志寄存器進行取反操作,CPLD會去檢測標志位的沿(上升沿下降沿都可),當CPLD檢測到這個沿,說明CPU的數據已經發送完成,CPLD會產生加載時鐘,并利用此時鐘將加載數據送入FPGA。CPLD只對邊沿進行檢測可以減少Local Bus的訪問周期,如果用0,1電平或者只用上升沿(只用下降沿),CPU傳送完數據后,需要先讀標志寄存器的值,再對標志位進行操作,而用上升沿和下降沿,CPU只需要在第一次傳送數據完成后讀標志寄存器,隨后的數據傳送完成后只需要對其進行取反即可。實現程序如圖9所示。

評論