基于FPGA和DSP的微振動傳感器信號采集系統設計

2.2.2 EDMA3控制器

TMS320C6747內的EDMA3控制器是一個高效的數據傳輸引擎,可在沒有CPU參與的前提下,完成DSP存儲空間內的數據轉移,保證CPU核心專注于信號處理算法的運算。

EDMA3傳輸有3種觸發方式:事件觸發、連鎖觸發和CPU觸發。本系統設計選擇事件觸發,FPGA內FIFO的half_full輸出信號和DSP的GP4[2]相連,滿足條件會自動觸發一個EDMA請求,執行對應于參數RAM的數據傳輸。

EDMA3數據傳輸的控制通過設置參數RAM來實現。本系統設計設置OPT=0x0010000C。其中TCINTEN位置1,當最后傳輸事務完成之后會觸發DSP系統的EDMA中斷;STATIC位置1,在EDMA事務傳輸請求完成之后參數RAM不會被更新或者鏈接到別的參數RAM;SYNCDIM位置1,EDMA傳輸類型是二維,每一個傳輸請求傳輸BCNT x ACNT字節。

為使EDMA事件傳輸及中斷能夠被觸發并順利執行,本系統設計進行下列配置:

(1)GPIO4[2]配置為邊沿觸發,且打開中斷使能;

(2)對EDMA寄存器EESR相應位寫1,使EER相應位置1,使EDMA3CC監測外部觸發事件;

(3)配置EDMA的參數RAM并寫進配置寄存器,定義EDMA數據傳輸的參數;

(4)配置EDMA寄存器DMAQNUM,映射GP4[2]中斷對應的28號事件到隊列0;

(5)配置EDMA寄存器DRAE[1],使能EDMA傳輸完成產生的中斷;

(6)置EDMA寄存器IER相應位為1,使對應通道的傳輸完成能觸發EDMA中斷;

(7)DSP控制寄存器IER.NMIE置1,使能DSP所有非重啟的中斷;

(8)DSP控制寄存器CSR.GIE置1,打開DSP中斷的總開關。

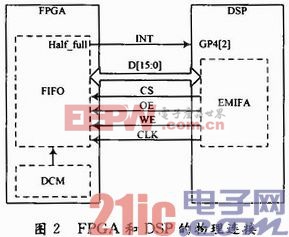

2.3 FPGA和DSP接口

系統設計采用FPGA和DSP雙核心,FPGA在并行運算方面有很高的效率,可負責控制信號的采集和預處理,而DSP擅長信號處理,負責信號的算法,保證系統的高效運行。FPGA和DSP的接口設計是保證兩者進行有效通信的關鍵。

本系統設計中DSP通過EMIFA和FPGA相連的物理接口如圖2所示。接口的信號線可分3部分:DSP對FPGA的控制線,FPGA通知DSP的中斷信號線和數據線。本文引用地址:http://www.104case.com/article/189702.htm

(1)控制線:在FPGA內部和DSP相連的是一個輸出FIFO,它的片選信號、時鐘信號和寫使能信號對應于TMS320C6747的信號EMA_CS3,EMA_ CLK,EMA_WE信號;而讀使能信號由EMA_OE,EMA_CS3和EMA_CLK共同產生,因為EMIFA的每一個讀時序包含多個EMA_CLK時鐘周期,在EMA_OE有效電平期間,FIFO的讀使能信號只能持續一個時鐘周期,否則多個數據將被讀出。

(2)中斷信號線:FIFO的信號線half_full和C6747的其中一個通用管腳GP4[2]相連,通過配置GPIO的配置寄存器SET_RIS_TRIG45,CLR_ FAL_TRIG45和BINTEN,GPIO4[2]電平由低到高的變化將會產生中斷。

(3)數據線:EMIFA的數據線是16位,12位的FIFO的輸出數據線直接和EMIFA的EMA_D低12位相連,在FPGA中配置與EMA_D高4位相連的管腳一直為0。

3 軟件設計

系統軟件設計包括FPGA模塊和DSP模塊的軟件流程控制,FPGA模塊內部主要是FIFO設計,控制數據的采集以及配合DSP進行通信,而在DSP模塊中主要包含EDMA數據傳輸控制和算法處理。

3.1 FPGA的FIFO

FPGA模塊采用Xilinx公司的XC4VSX35型號,其內部設計有DCM模塊和FIFO模塊。DCM模塊和外部的晶振相連,引入時鐘信號,通過DCM輸出時鐘信號給AD9235作時鐘信號以及FPGA內部FIFO的寫時鐘信號。FIFO模塊設有相互獨立的讀寫時鐘,是異步讀寫方式,能夠協調模/數轉換模塊和DSP模塊之間的工作,把數據從模/數轉換模塊的輸出轉移到DSP模塊。

FIFO模塊采用XC4VSX35內部的Block RAM,通過IP核配置的方式,生成所需的FIFO緩沖存儲器,FIFO的寫入時鐘由FPGA內部的DCM提供。在寫入時鐘的控制下AD9235的輸出數據寫入FIFO緩沖器,當FIFO內數據數量達到設定值時,FIFO的half_full信號線電平由低轉高,以GPIO中斷的方式觸發DSP的EDMA事務進行數據轉移。圖3是ISE7.1中FIFO的仿真時序圖。

fpga相關文章:fpga是什么

傳感器相關文章:傳感器工作原理

干涉儀相關文章:干涉儀原理

光纖傳感器相關文章:光纖傳感器原理

評論