基于DSP+FPGA的紅外移動目標識別跟蹤系統設計

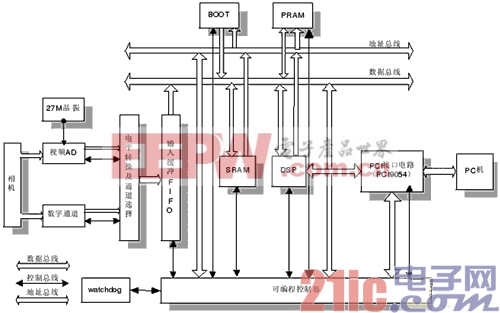

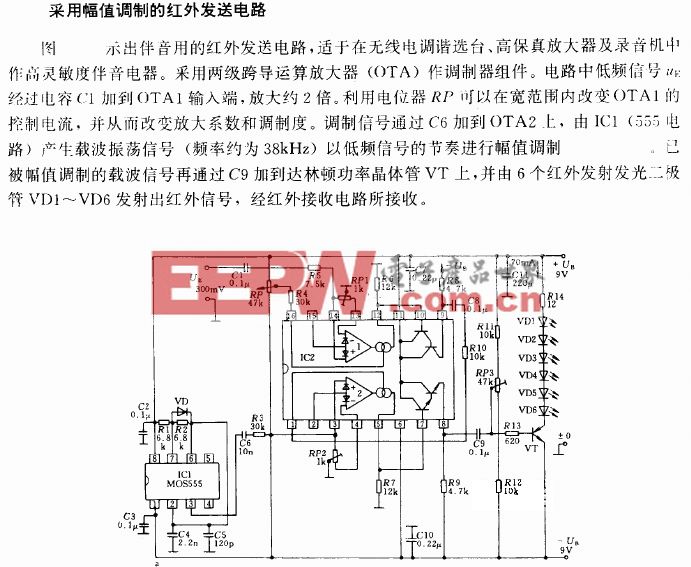

系統硬件設計系統硬件原理框圖如圖2所示,為了設計和描述的方便,我們把硬件模塊的電路結構劃分為以下幾個單元:視頻接口單元、輸入輸出FIFO視頻圖像存儲器、數字圖像處理單元(DSP)、可編程控制器、與PC的PCI接口電路等。

圖2系統硬件原理框圖

1視頻接口單元

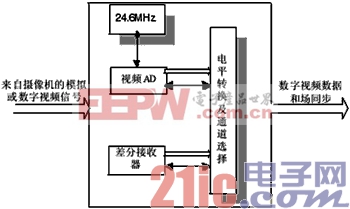

紅外運動目標識別與跟蹤系統的視頻源是紅外攝像機提供的視頻信號。紅外攝像機有兩路視頻輸出,即模擬視頻輸出和數字視頻輸出。本系統要求硬件模塊對兩路視頻信號都能夠進行處理。因此,必須對輸入視頻信號進行預處理,為數字圖像處理單元(DSP)提供必要的視頻數據和視頻同步數據。視頻接口單元框圖如圖3所示。

圖3視頻接口單元框圖

2輸入輸出緩沖FIFO

設置輸入輸出緩沖FIFO的目的是在高速器件和低速器件之間設置一個緩沖區,可以避免高速器件因等待低速器件的數據而使系統的效率降低。A/D芯片送出的數字信號的時鐘頻率約為12MHz(模擬通道時鐘12.51MHz,數字通道時鐘12MHz),而處理卡上DSP的總線頻率高達50MHz,兩者差異較大,所以采用輸入輸出緩沖FIFO是必要的。基于以上考慮,最終選用Cypress公司的CY7C4275.它的容量為32K×18,最大存取速度可達到l0ns.

3可編程控制器(FPGA)

在本系統中,FPGA控制了絕大部分單元,包括通道選擇/電平轉換芯片、輸入輸出FIFO、SRAM、DSP、PCI接口電路等。利用FPGA芯片的系統內可編程(ISP)性能,完成所有DSP外圍芯片的控制邏輯;并在其中設置狀態寄存器、命令字寄存器和專用寄存器,完成與主機的實時通信,接收主機傳送的命令信息和向主機傳送所需要的狀態信息。

在本系統中,數字信道為14bit,模擬為8bit,需要由FPGA對信號進行第一次裝配(區別于DSP為了顯示而對圖像按FGB格式進行的第二次裝配),即將數字/模擬信號/數據均轉換為16bit的數據,然后將兩個16bit數據裝配成一個32bit的數據。

4數字圖像存儲器(SRAM)

紅外動目標識別與跟蹤系統要完成對運動目標的識別與跟蹤。其實現算法必然涉及到對多幀(差分處理,至少兩幀)視頻圖像的處理。為了給實現算法提供較為充裕的存儲空間,我們選用的存儲器能容納6場視頻圖像。因此,最后選用的存儲器是Giga Semiconductor公司的兩片GS74116,其每片容量為256K×16bit,存取速度為15ns.考慮到我們視頻圖像每場的數據量為76800像素,兩片512K的SRAM可以存下至少6張視頻圖像。在本系統中,我們設置了4幀圖像存儲空間,其余空間用于存放目標小圖、DSP裝配數據等,數據空間具體地址分配如圖4所示。

圖4 SRAM數據空間分配5數字圖像處理模塊(DSP)

評論