基于SOPC的異步串行通信IP核設計

4實驗驗證

系統硬件介紹

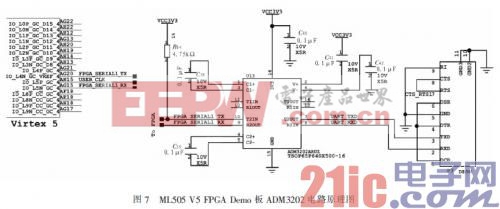

本文采用Xilinx公司提供的ML505 V5 FPGA Demo板作為SoPC系統硬件平臺。ML505 FPGA演示驗證板主要由一塊Virtex-5 XC5VLX50T FPGA構成,此外還包括RAM、Flash、以太網接口芯片、USB接口芯片以及ADM3202 RS-232電平轉換芯片等外圍擴展芯片,其中ADM3202電路原理圖如圖7所示。

實驗采用Xilinx公司ISE工具完成UART IP核的邏輯綜合和仿真,仿真波形如圖8所示,發送數據為0x01.UART IP核仿真通過后,用EDK工具提供的Peripheral Import Wizard生成一個采用PLB Slave Single模塊的自定義IP核框架。在該IP核目錄下的user_logic.v文件中例化波特率模塊、發送模塊、接收模塊和寄存器組,并增加相應總線訪同邏輯后即生成了本文設計的UART IP核。

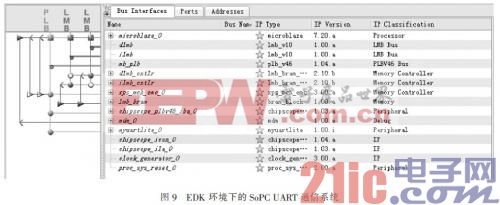

用EDK工具中的Base System Builder wizard新建一個如圖3所示的SoPC系統,如圖9所示。在Port界面下將UART IP核的收發管腳定義為External,并在UCF文件中加入收發管腳的管腳映射描述。在Address界面下生成UART IP核的地址空間,UART通信測試程序將通過該地址空間訪問UART IP核。用EDK工具中Hardware菜單下Generate Bit Stream命令生成該SoPC系統的FPGA配置文件。用該配置文件配置ML505板載FPGA后,即生成了SoPC UART通信系統硬件。

用EDK工具中的Xilinx SDK軟件開發工具編寫相應的UART通信測試程序,編譯后將程序下載至MicroBlaze處理器程序空間。將ML505板串口與PC機串口連接后運行UART通信測試程序,在PC機上可以觀察到此UART通信系統可以正確的發送和接收UART數據,證明了該UART IP核工作正常。

5結論

文中詳細介紹了一種基于SoPC概念的UART IP核的設計。通過將Xilinx公司提供的PLB Slave Single模塊和本文設計的UART邏輯模塊結合,快速搭建了一個滿足PLB總線接口要求的UART IP核,仿真與綜合結果表明該UART IP核各項功能均達到預期要求。該設計方法既采用了成熟的商業IP核,也利用總線接口模塊將用戶自定義IP核與商業IP核連接成為一個完整的SoPC系統。該方法增加了系統的靈活性、擴展性,同時縮短了系統開發時間,降低了系統開發難度,可為其他嵌入式系統的開發提供有益的參考。

評論