基于Virtex-6 FPGA的雙緩沖模式PCIe總線設計方案和

2 軟件無線電平臺設計

軟件無線電基于可編程、可重構的通用硬件平臺,通過加載不同的軟件實現不同的無線電功能,廣泛應用于軍用和民用領域。為了能夠實現復雜的算法,其平臺需要具備高速數據交換和實時信號處理的能力。該設計參考Xilinx ML605開發套件,基于Xilinx Virtex6 LX240T FPGA芯片,通過增加相應的模塊搭建通用的軟件無線電平臺。

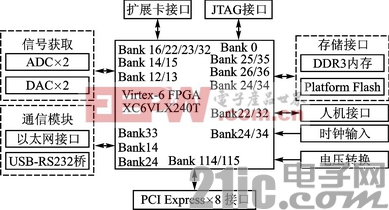

軟件無線電原理框圖如圖3所示。信號獲取模塊采用兩片ADC和DAC以實現IQ兩路信號的數模轉換;通信模塊由以太網和USBRS232接口組成;擴展卡可以是射頻發射機或接收機,通過擴展卡接口與母板相連;JTAG接口提供在線編程和內部測試功能;存儲器件包括512 MB DDR3內存和128 MB平臺Flash,分別用于動態數據存儲和配置FPGA;人機接口由LED/LCD、按鍵和開關等元件組成,實現人機對話;200 MHz有源晶振和SMA時鐘接口組成時鐘輸入模塊,向FPGA提供時鐘基準;8通道PCIE接口和IP核實現平臺與PC間高速數據交換。

圖3 軟件無線電原理框圖

3 雙緩沖模式PCIE總線設計

3.1 PCIE驅動設計

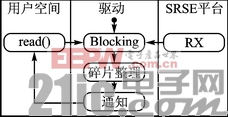

PC端基于Linux(Ubuntu 10.10)操作系統。該操作系統免費開源,安全穩定靈活,適合低成本軟件開發。驅動程序包含數據流接口和控制接口。數據流接口用于Linux用戶空間和SRSE平臺間高速的數據交換;控制接口使用戶可以觀察和配置SRSE平臺寄存器,例如通過控制接口,用戶可以在PC端改變SRSE平臺的調諧頻率等參數。數據流接口是雙向獨立的,支持雙/單工,即可以同時讀和寫數據。以數據發送(從PC到SRSE)為例,用戶空間調用write()函數將任意數量的數據發送至驅動,驅動整理數據碎片以滿足PCIE對數據對齊和傳輸塊數據量的要求。當數據滿足4096字節,驅動將數據塊發送至Root Complex并保留已發送數據的列表,等待接收來自SRSE平臺的寫操作中斷。PCIE驅動數據接收的原理如圖4所示。當用戶空間調用read()函數或者驅動接收到來自PCIE設備的數據時,驅動初始化讀操作。驅動程序將保持阻塞(blocking),直到用戶空間調用read()函數,并且已接收到足夠的數據包,從而能夠填滿read()請求的數據量。碎片整理模塊對已接收的數據進行整理,然后將數據塊返回至用戶空間,并通知其解除驅動阻止。

圖4 PCIE驅動中的數據接收

評論