基于FPGA的心音信號(hào)采集系統(tǒng)設(shè)計(jì)

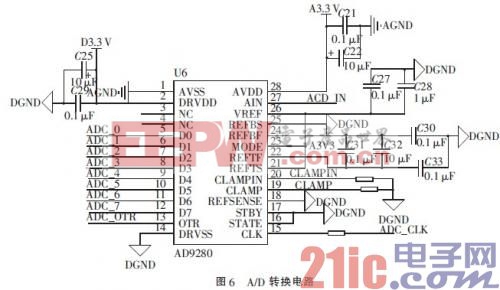

2.3 A/D轉(zhuǎn)換電路

AD9280是一款單芯片、8 bit模數(shù)轉(zhuǎn)換器(ADC),采用單電源供電,內(nèi)置一個(gè)片內(nèi)采樣保持放大器和基準(zhǔn)電壓源。它采用多級(jí)差分流水線架構(gòu),數(shù)據(jù)速率達(dá)32 MS/s,在整個(gè)工作范圍內(nèi)保證無(wú)失碼。輸入經(jīng)過(guò)設(shè)計(jì),使成像和通信系統(tǒng)的開(kāi)發(fā)更加輕松。用戶可以選擇各種輸入范圍和偏移,并可以通過(guò)單端或差分方式驅(qū)動(dòng)輸入。AD9280具有一個(gè)片上可編程基準(zhǔn)電壓源。也可以使用外部基準(zhǔn)電壓,以滿足應(yīng)用的直流精度與溫度漂移要求。采用+2.7 V~+5.5 V電源供電,非常適合高速應(yīng)用中的低功耗操作。額定溫度范圍為-40℃~+85℃工業(yè)溫度范圍。A/D轉(zhuǎn)換電路如圖6所示。

2.4 FPGA控制串口通信

結(jié)合項(xiàng)目的現(xiàn)有設(shè)備DB2C8核心板,將信號(hào)放大電路和A/D轉(zhuǎn)換電路經(jīng)過(guò)DB2C8核心板的擴(kuò)展口,把A/D轉(zhuǎn)換的數(shù)據(jù)傳送到FPGA芯片EP2C8Q208,A/D轉(zhuǎn)換的采樣時(shí)鐘由FPGA來(lái)控制,利用FPGA的FIFO存儲(chǔ)器存儲(chǔ)A/D轉(zhuǎn)換的數(shù)據(jù),然后控制串口通信的波特率為115 200 b/s,進(jìn)行實(shí)時(shí)傳輸。FPGA仿真波形如圖7所示。FIFO為異步讀寫,F(xiàn)IFO寫時(shí)鐘速率為8 kHz,讀速率為60 MHz,串口通信的波特率設(shè)置為115 200 b/s,如圖7所示,PORT_txd為串口輸出,q為FIFO的讀數(shù)。

本采集系統(tǒng)在FPGA的控制下能夠快速、便捷地采集心音信號(hào)數(shù)據(jù),由采集的數(shù)據(jù)畫出的波形如圖8所示。本系統(tǒng)數(shù)據(jù)傳輸速率高,能在噪聲背景下提取出有用的心音信號(hào),使得心音的采集更加方便,心音庫(kù)的建立變得切實(shí)可行。

fpga相關(guān)文章:fpga是什么

電荷放大器相關(guān)文章:電荷放大器原理

評(píng)論