基于FPGA的多功能頻率計的設計與實現

4 MC8051 IP Core軟件設計流程

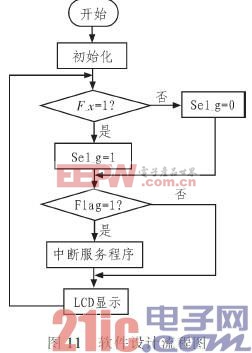

系統軟件設計流程如圖11所示。

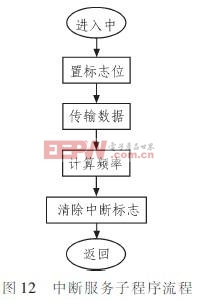

中斷服務子程序如圖12所示。

5 結論

文中采用Altera的cyclone II系列的EP2C8Q208C8這款FPGA芯片。設計中使用了Verilog語言對各個模塊的描述設計。文中提出的數字頻率計設計方案采用等精度的測量算法,以先進的FPGA可編程邏輯器件作為核心控制及運算電路單元可達到很高的測量精度要求,8051 IP Core嵌入到FPGA芯片系統,與測頻模塊共用同一個FPGA芯片,和傳統的頻率計相比大大減小了電路板的尺寸,同時增加了系統的可靠性、設計靈活性和可更改性。實現了數字系統的軟件化。加入LCD液晶顯示,使測量效果更加直觀。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鎖相環相關文章:鎖相環原理

評論