基于FPGA的多功能頻率計的設計與實現

2 等精度測頻原理及FPGA設計

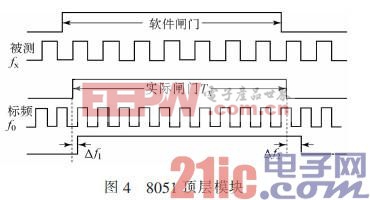

等精度測量的一個最大特點是測量的實際門控時間不是一個固定值,而是一個與被測信號有關的值,剛好是被測信號的整數倍,即與被測信號同步。這樣就達到了在整個測試頻段的等精度測量。等精度測頻的核心思想就是通過閘門的信號與被測信號同步,將閘門時間τ控制為被測信號周期長度的整數倍。測量時,先打開預置閘門,當檢測到被測信號脈沖沿到達時,標準信號時鐘開始計數。預置閘門關閉時,到達時才停止,完成被測信號整數個周期的測量。測量的實際閘門時間與預置閘門時間可能不完全相同,但最大差值不超過被測信號的一個周期。設實際閘門時間為τ,被測信號周期數為Nx,標準信號頻率為fs、計數值為Ns,則被測信號的頻率測量值為:

由于實際閘門時間τ為被測信號周期的整數倍,因此Nx是精確的,而標準信號時鐘的計數值Ns則存在誤差△Ns(|△Ns|≤1),即標準信號計數的真實值應Ns+△Ns。

由此可知被測信號的頻率真實值為:

可以看出,相對誤差與被測信號本身的頻率特性無關,即對整個測量頻率域而言,測量精度相等,因而稱之為“等精度測量”。標準信號的計數值Ns越大,則測量相對誤差越小,即提高門限時間τ和標準信號頻率fs可以提高測量精度。在精度不變的情況下,提高標準信號頻率可以縮短門限時間,提高測量速度。在計數允許時間內,同時對標準信號和被測信號進行計數,再通過數學公式推導得到被測信號的頻率。由于門控信號是被測信號的整數倍,就消除了對被測信號產生的±1誤差,但是會產生對標準信號±1的誤差。如圖4所示。

系統中,采用了標準信號源的精度很高,可以達到一個很高的測量精度,本系統采用晶體作為標準信號源,因此可以達到很高的精度。

3 FPAG設計模塊

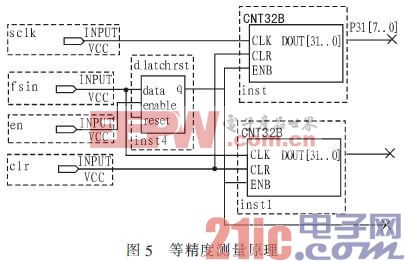

本系統以Verilog HDL硬件描述語言為工具,在傳統的等精度測量原理基礎上進行了改進和優化。增加了測量占空比的功能,同時由FPGA內部產生清零信號,節省了資源。FPGA核心模塊如圖5所示。FPGA部分主要由門控信號產生模塊、計數器控制模塊、計數器模塊、鎖存器、中斷輸出、數據選擇輸出、頂層模塊組成。

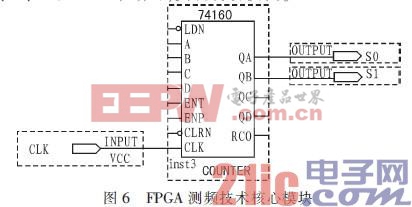

門控信號:時鐘信號源產生頻率很高的時鐘信號,經過分頻以后,得到頻率為1 Hz、1 kHz、1 MHz和50 MHz 4種時鐘信號,這些信號作為時基電路輸入信測量開始,TW為1s,計數器對被測信號fsin進行計數,如果計數超過規定值9999,產生溢出信號OVERFLOW,在其作用下,量程轉換電路輸出信號SW狀態發生變化,自動完成一次量程的換擋,同時將TW調整為0.1s,計數器重新計數。如果還有溢出信號,繼續量程換擋,調整TW,直到不再有溢出信號為止。其中74160接成了一個同步四進制加法計數器,如圖6所示。它的時鐘輸入端CLK與計數器輸出端OVERFLOW(溢出)連接,在溢出信號作用下,量程轉換電路輸出端S1、S0依次輸出00、01、10和11 4個編碼,實現自動換擋。

計數器控制模塊:門控信號啟動(上升沿)后,在被測信號的上升沿啟動計數允許模塊,允許計數器計數;門控信號關閉(下降沿)后,在被測信號的下一個上升沿關閉計數允許模塊,停止計數,從而保證了門控信號是被測信號的整數倍,達到了等精度的目的。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鎖相環相關文章:鎖相環原理

評論