基于FPGA的可逆數制轉碼器設計

2.3 12 b可逆轉碼器的結構設計

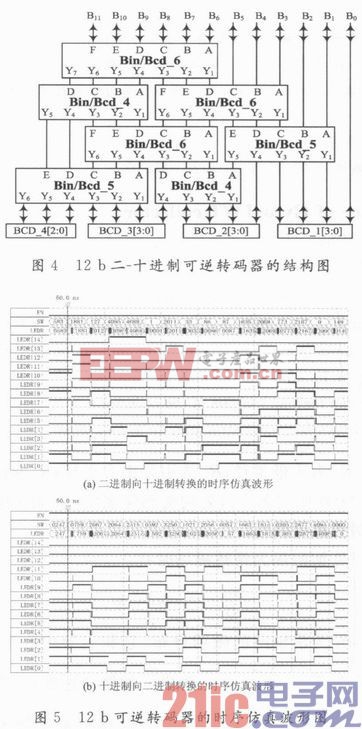

根據二-十進制可逆轉碼算法,使用上節中得到的4 b,5 b和6 b三種二-十進制可逆轉碼單元模塊,構造出12 b二-十進制(BCD)可逆轉碼器結構如圖4所示,轉碼單元模塊的多余輸入端要接地,多余輸出端懸利于轉碼器的位數擴展,也可以通過轉碼器的使能端BD/DB的取值分別實現從二進制到十進制和從十進制到二進制的數制轉換。本文引用地址:http://www.104case.com/article/189669.htm

3 二-十進制可逆轉碼器的設計驗證

3.1 可逆轉碼器的時序仿真

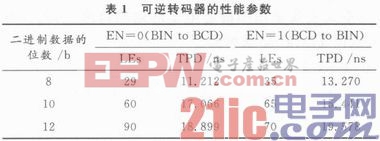

使用QuartusⅡ9.1(Full Version)開發工具;對于圖4中二-十進制(BCD)可逆轉碼器,在Altera公司的FPGA(EP2C35F672C6)芯片上進行了設計驗證,驗證結果完全達到了既定的設計目標;時序仿真結果如圖5所示。在圖5(a)中,使能信號EN=0,轉碼器實現12 b二進制數向4位十進制(BCD)數據的轉換,SW是輸入12 b二進制數,LEDR是輸出的4位十進制(BCD)數(15 b,最大值是4 095);在圖5(b)中,使能信號EN=1,轉碼器實現15 b十進制數(最大4 095)向12 b二進制數據的轉換,SW是輸入15 b十進制數(BCD),LEDR是輸出的12 b的二進制數。

3.2 可逆轉碼器的性能分析

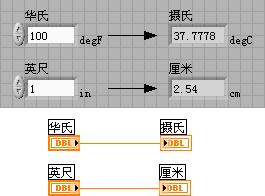

使用QuartusⅡ9.1開發工具和DE2開發板;對于所設計可逆數制轉碼器通過模塊的參數配置,分別測試了轉碼器在完成8 b、10 b和12 b轉碼情況下的硬件實現代價(占用邏輯單元數LEs)和最大路徑延遲(TPD),測試結果見表1。

表1表明,可逆轉碼器的數據位寬愈大轉碼器就越復雜,使用的單元模塊就越多,實現代價增大,路徑延遲也會增大,12 b可逆轉碼器的最高時鐘頻率只有50 MHz,而8 b的可逆轉碼器最高時鐘頻率可以達到75 MHz。

4 結語

文中提出以3種功能模塊來構造二-十進制(BCD)可逆轉碼器的設計方法,通過端口參數配置和模塊重構就能實現不同位數的數據在二進制和十進制(BCD)之間相互轉換。從而使基于FPGA的二-十進制(BCD)轉碼器的構建變得簡單、靈活。可逆轉碼器在EP2C35F672C6芯片上的驗證結果也充分證明了這種設計思路的可行性;如果進一步在轉碼器中插入寄存器而形成流水線結構,那么轉碼器的運算速度就會有更大提升。

評論