基于FPGA的可逆數(shù)制轉(zhuǎn)碼器設(shè)計(jì)

2.2 可逆轉(zhuǎn)碼器的功能模塊設(shè)計(jì)

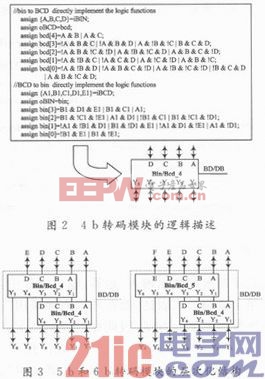

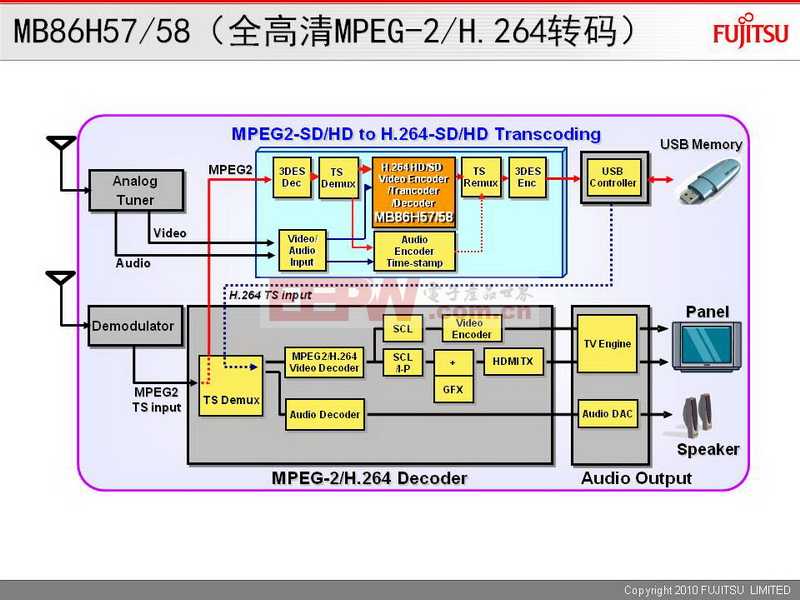

上述基于FPGA的二-十進(jìn)制(BCD)可逆轉(zhuǎn)碼器設(shè)計(jì)方案,關(guān)鍵就在于要做好最底層模塊(4 b轉(zhuǎn)碼模塊)的優(yōu)化設(shè)計(jì),對(duì)4 b轉(zhuǎn)碼模塊的不同Verilog HDL描述方式也會(huì)帶來(lái)不同的實(shí)現(xiàn)代價(jià);通過(guò)不同描述方式比較最終確定使用結(jié)構(gòu)描述來(lái)實(shí)現(xiàn)4 b可逆轉(zhuǎn)碼模塊(Bin/Bcd_4),根據(jù)參考文獻(xiàn)[4-5,10],采用卡諾圖和Multisim軟件化簡(jiǎn)得到最簡(jiǎn)邏輯函數(shù)式如圖2所示。再通過(guò)4 b轉(zhuǎn)碼模塊層次實(shí)例化分別構(gòu)造5 b轉(zhuǎn)碼模塊(Bin/Bcd_5)和6 b轉(zhuǎn)碼模塊(Bin/Bcd_6),如圖3所示。本文引用地址:http://www.104case.com/article/189669.htm

評(píng)論