多慣組脈沖輸出同步計數系統設計

2.2 時鐘分頻模塊設計

本系統采用50 MHz有源晶振,EP2C8Q208C8N內部擁有兩個鎖相環,通過倍頻使頻率達到400MHz,然后連接一個分頻模塊為狀態機提供周期為4ms的計數值鎖存信號(clk_lock)和一個狀態機跳轉觸發信號(clk_state)。

2.3 狀態機模塊設計

狀態機模塊主要包括兩個部分:數據處理部分和FIFO控制邏輯部分。

2.3.1 狀態機的數據處理部分

狀態機在計數值鎖存信號(clk_lock)上升沿到來時會鎖存計數器此刻的計數值,并在狀態機的下一個狀態將計數值存儲到data-new的寄存器型變量中并進行求差運算,接著將被減數與減數在下一個狀態進行更新,最后將求出來的差值交給FIFO控制邏輯進行發送。每個計數單元計數值求差的狀態機原理圖如圖3所示。本文引用地址:http://www.104case.com/article/189660.htm

2.3.2 狀態機的FIFO控制邏輯部分

FPGA控制邏輯的主要作用足通過其內部的狀態機直接操作CY68013的FIFO來進行讀寫控制。SLOE、SLRD和SLWR作為芯片的讀寫信號與使能控制信號。INPKTEND是FPGA主動命令USB芯片向上位PC發送數據的控制端(當FIFO上的數據小于規定大小而又要強制上傳給PC時使用)。FD為雙向的數據傳輸接口。FLAGA、FLAGB、FLAGC、FLAGD四個標志位能夠指示FIFO的空滿程度,為數據的連續存取提供了可靠的保證。FPGA_ADR0和FPGA ADR1用于選擇內部4個緩沖端點之一。IFCLK提供時鐘信號(僅用于同步Slave FIFOs模式)。FPGA的引腳控制這些端口,達到對USB端的存儲FIFO進行操作的目的。由于異步Slave FIFOs模式的讀寫狀態簡單,穩定性好。本系統選擇異步方式來讀取FIFO。

實現異步Slave FIFO的寫操作的狀態機如圖7所示。其狀態轉移進程如下:

IDLE:此狀態為空閑狀態,什么也不做;當寫事件發牛時(即CLK_LOCK的上升沿到來時),進狀態1;

狀態1:使FIFOADR[1:0]指向IN FIFO(即就是選擇CY68013的四個大數據量FIFO中的一個,固件程序已將此FIFO配置為寫模式),進狀態2;

狀態2:如果FIFO滿標志為假(即FLAGC引腳為高電平時),則進狀態3;否則在本狀態等待;

狀態3:驅動數據到數據線上,使SLWR有效(低電平),一個CLK_STATE后再無效(高電平),以使FIFO寫指針遞增,進狀態4;

狀態4:如需傳輸更多的數,返回狀態2,否則進狀態IDLE。

狀態跳轉示意圖如圖4所示:

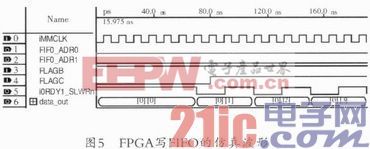

使用QuartusII對FIFO的控制邏輯進行時序仿真如圖5所示。

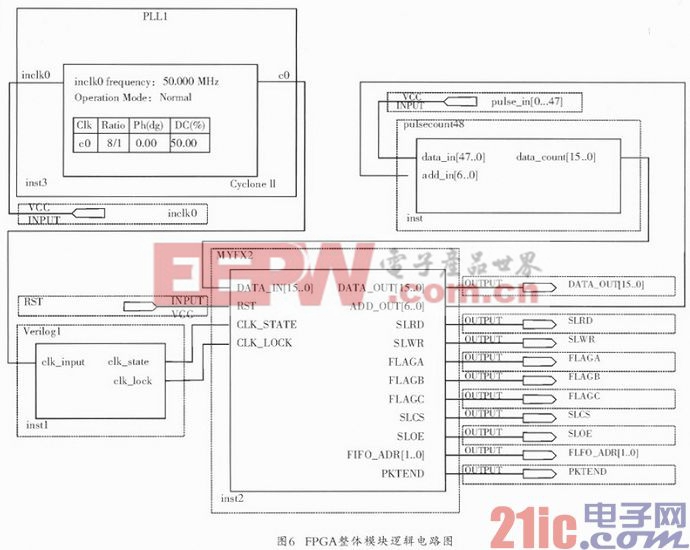

2.4 FPGA整體模塊設計

FPGA整體模塊邏輯電路圖如圖6所示。

評論