多慣組脈沖輸出同步計(jì)數(shù)系統(tǒng)設(shè)計(jì)

摘要:為滿足某慣導(dǎo)設(shè)備生產(chǎn)廠家對多個(gè)慣組產(chǎn)品進(jìn)行同時(shí)測試的需求,設(shè)計(jì)了一種對于多路脈沖信號(hào)同步計(jì)數(shù)的測試系統(tǒng)。(方法)測試系統(tǒng)以FPGA芯片和USB芯片CY68013為核心,對4個(gè)慣導(dǎo)組件輸出的48路脈沖信號(hào),每路進(jìn)行無縫計(jì)數(shù),每4ms為一個(gè)計(jì)數(shù)單元。并利用USB總線將每一個(gè)計(jì)數(shù)單元的計(jì)數(shù)值上傳到測控計(jì)算機(jī),上位機(jī)程序進(jìn)行實(shí)時(shí)的處理、保存和顯示。(方法)測試系統(tǒng)滿足了對多個(gè)慣組產(chǎn)品同時(shí)測試的要求,提高了測試效率。

關(guān)鍵字:慣導(dǎo)組件;USB;CY68013;FPGA

慣組產(chǎn)品是現(xiàn)代慣導(dǎo)系統(tǒng)最核心的信息源,由陀螺儀和加速度計(jì)組合而成。慣組產(chǎn)品工作時(shí)直接輸出脈沖信號(hào)。測試過程采用專用測試平臺(tái),將產(chǎn)品固定在帶溫箱的三軸轉(zhuǎn)臺(tái)上,通過在不同的溫度下改變轉(zhuǎn)臺(tái)的位置和速率,由測試系統(tǒng)對其輸出的脈沖信號(hào)進(jìn)行計(jì)數(shù),再對計(jì)數(shù)值根據(jù)數(shù)學(xué)模型進(jìn)行處理,從而得到慣組產(chǎn)品的性能參數(shù)。由于溫度是影響慣導(dǎo)組件的主要因素之一,所以需要在多個(gè)溫度點(diǎn)下,對其進(jìn)行多次測試。而每個(gè)溫度點(diǎn)需要4個(gè)小時(shí)的保溫。因而完成一個(gè)產(chǎn)品的標(biāo)定,一般需要三天左右的時(shí)間才能完成。針對這種情況,本文提出了一種多慣組同時(shí)測量的方案,利用FPGA對脈沖信號(hào)進(jìn)行采集,再通過USB總線把采的數(shù)據(jù)發(fā)送到PC機(jī)上進(jìn)行數(shù)據(jù)歸算。與傳統(tǒng)的測量系統(tǒng)相比,本系統(tǒng)可以對4個(gè)慣導(dǎo)組件的48路脈沖數(shù)據(jù)進(jìn)行同步計(jì)數(shù)并輸出,進(jìn)而有效地縮短測試周期,提高測試效率。

1 測試系統(tǒng)組成

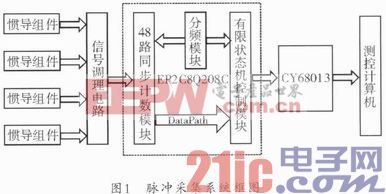

多慣組脈沖測試系統(tǒng)是由下位機(jī)和上位機(jī)兩個(gè)部分構(gòu)成。下位機(jī)由FPGA和USB接口電路組成,實(shí)現(xiàn)對脈沖信號(hào)的計(jì)數(shù)和數(shù)據(jù)的接收。上位機(jī)是MFC程序設(shè)計(jì)的界面,對接收到的數(shù)據(jù)進(jìn)行實(shí)時(shí)的處理、顯示和保存。由于本系統(tǒng)是同時(shí)接收4套慣組48路脈沖信號(hào),所包含的計(jì)數(shù)器個(gè)數(shù)多,計(jì)數(shù)頻率高,并且分別對48路信號(hào)獨(dú)立測量,要求較高的可靠性,所以系統(tǒng)采用FPGA來實(shí)現(xiàn)控制邏輯及計(jì)數(shù)模塊的功能。系統(tǒng)選用Altera公司的Cyclone IIEP2C89208C8N型號(hào)的FPGA芯片。在數(shù)據(jù)傳輸方面,選用Cypress公司的FX2LP CY68013芯片作為USB傳輸模塊。采集系統(tǒng)框圖如圖1所示。

在圖1中,通過Verilog語言對48路同步計(jì)數(shù)模塊進(jìn)行設(shè)計(jì),實(shí)現(xiàn)對48路脈沖信號(hào)的同步計(jì)數(shù),將接收到的數(shù)據(jù)通過USB芯片CY68013發(fā)送到PC機(jī),由PC機(jī)對接收到的數(shù)據(jù)進(jìn)行處理,脈沖信號(hào)的計(jì)數(shù)是由無縫計(jì)數(shù)器,每隔4ms向48路計(jì)數(shù)模塊發(fā)送相應(yīng)的地址,獲得48路脈沖計(jì)數(shù)模塊的計(jì)數(shù)值,再通過USB總線把數(shù)據(jù)發(fā)送到PC機(jī)上。

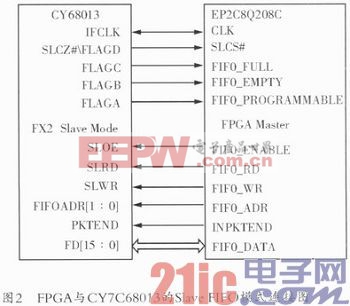

FX2LP CY68013芯片有PORTS、Slave FIFOs和GPIF三種接口方式:PORTS模式以CY68013自帶的8051核來進(jìn)行端口FIFO的讀寫,其優(yōu)點(diǎn)是開發(fā)簡單,缺點(diǎn)是傳輸速度有限;Slave FIFOs模式是使用外部芯片的邏輯來直接操作端口FIFO,其優(yōu)點(diǎn)是端口FIFO操作靈活,缺點(diǎn)是傳輸速度依賴于外部控制邏輯的速度;GPIF模式是使用波形編輯工具生成的波形信號(hào)來進(jìn)行端口FIFO的讀寫,其優(yōu)點(diǎn)是傳輸速度最高,缺點(diǎn)是讀寫邏輯單一,不容易靈活控制。因?yàn)槭菍?8路脈沖信號(hào)進(jìn)行實(shí)時(shí)采樣計(jì)數(shù),且每一路脈沖信號(hào)采用一個(gè)16位計(jì)數(shù)器,采樣周期為4毫秒,即每秒要采集250次。但在實(shí)際使用中發(fā)現(xiàn),在PORTS模式下,由于8051內(nèi)核執(zhí)行速度有限,在極短的中斷時(shí)間內(nèi)有時(shí)會(huì)不能完成其數(shù)據(jù)處理和傳輸?shù)娜蝿?wù),此種狀態(tài)下USB端就會(huì)出現(xiàn)死循環(huán)狀態(tài)。但在Slave FIFO或CPIF模式下,傳輸和接收的端口將不經(jīng)過8051內(nèi)核干涉即可同片外高速互傳數(shù)據(jù),從而提高接收發(fā)送串行信號(hào)的效率與可靠性。由于GPIF模式下的編輯波形只能進(jìn)行讀寫操作,而在Slave FIFOs的模式下狀態(tài)機(jī)可以對數(shù)據(jù)進(jìn)行簡單的處理。因此,本系統(tǒng)使用Slave FIFOs的傳輸模式。

2 系統(tǒng)的FPGA設(shè)計(jì)

2.1 48路脈沖計(jì)數(shù)模塊設(shè)計(jì)

系統(tǒng)的48路脈沖計(jì)數(shù)模塊設(shè)計(jì)是通過使用Verilog語言編寫的16位計(jì)數(shù)器,可以對慣導(dǎo)組件輸出的信號(hào)分別進(jìn)行不間斷計(jì)數(shù),計(jì)數(shù)值讀取過程不影響計(jì)數(shù)器的正常計(jì)數(shù),該模塊data_in[47…0]是48路慣導(dǎo)組件的脈沖輸入,add_in [6…0]是每個(gè)脈沖輸入通道的地址,data_out[15…0]是計(jì)數(shù)單元的計(jì)數(shù)值輸出。

評論