基于FPGA的雙備份多路數據采集存儲系統的設計與實

4 測試試驗

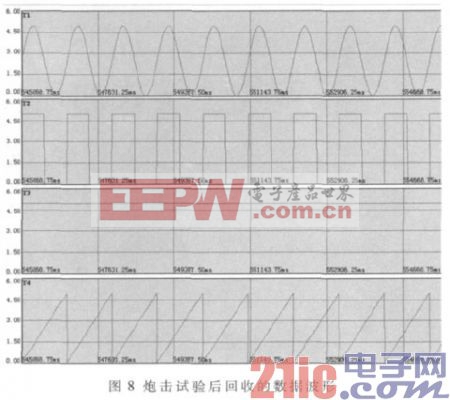

對數據采集存儲系統進行炮擊試驗,其目的是為了考核記錄器的外部結構以及內部電路板的抗過載能力。試驗前,采編器采集標準的模擬彈上信源(正弦波、方波、直流量、鋸齒波……依次循環),并存入存儲器,然后將整個系統安裝在飛行體中,飛行體以極高的速度著靶,測試采集存儲系統的沖擊過載能力。試驗后電路板正常無損壞,而其中一塊(B片)外部晶體振蕩器損壞,因此,存儲器采用雙時鐘源,正常情況下由晶體振蕩器提供時鐘源,在存儲器回收后讀取數據時,若晶體振蕩器損壞,可由地面測試臺提供的備用時鐘作為存儲器時鐘源,這樣就避免了回收存儲器后更換晶體振蕩器的麻煩。試驗完成后從A片存儲器中回收數據,并與試驗前的數據相比較,結果一致,再從B片存儲器中回收數據(由于外部晶體振蕩器損壞,需用備用時鐘源),與試驗前的數據相比較,其波形一致,如圖8所示。圖8中列舉了其中4個通道T1~T4的電壓信號,試驗表明,該系統具有很強的抗過載能力。

本文給出了基于雙備份存儲器的數據采集存儲系統的電路設計和控制邏輯設計。在工程實踐的基礎上,對多通道異步時分電路的通道串擾現象提出了可行性的解決方案,同時詳細地介紹了采用FPGA實現采集控制邏輯以及存儲邏輯的方法,也給出了采集控制邏輯的流程和存儲邏輯的設計流程。通過飛行試驗,該采集存儲系統采集了用來評估飛行器的各種技術指標的有用數據,實踐證明,雙備份設計有效的提高了數據回收的可靠性。

評論