基于FPGA的雙備份多路數據采集存儲系統的設計與實

3系統軟件設計

3.1采集控制邏輯的設計

對于多通道異步時分采集這種形式的電路,由于在電子開關切換的過程中存在著串擾,信號受到該串擾后,濾波放大器的輸出在ADC采樣前未穩定至其應有的精度,就會對ADC的采樣有影響,從而影響采集精度。所以,為了解決串擾問題,只有在實踐的基礎上,靠經驗去選擇合適的運放,或者是通過硬件與系統軟件優化相結合的方法尋找解決途徑。

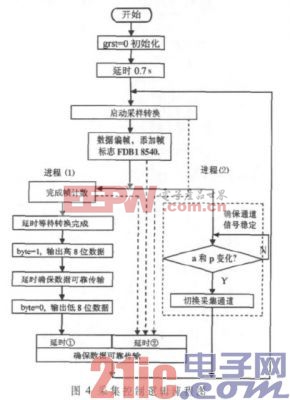

在確保系統采樣率的前提下,本設計通過硬件與軟件相結合的方法來解決串擾問題。硬件上采集模塊選擇SR(壓擺率)較高的運放LF247作為濾波跟隨器,軟件上則以并行的工作方式確保采樣前采樣通道信號的穩定,即在時序設計上,主程序中采用了兩個進程:(1)完成數據的轉換、幀計數和數據的傳輸; (2)根據幀計數frame_cnt控制通道地址信號a和p進行通道切換。這兩個進程并行執行。

FPGA采集控制邏輯流程圖如圖4所示。其中,a為通道選擇輸出,接ADG506的通道選擇控制端(A3~A0);P為ADG506選通信號,接ADG506的片選端(EN)。

由于存儲器采用雙備份設計以及對兩片存儲器的寫入操作完全相同,故采集控制邏輯中分別有控制A、B片存儲器的控制信號wrclkA和wrclkB,數據通過MAdata、MBdata分別存入存儲器的A、B片中,如圖5所示。

圖5[3]是FPGA的時序轉換圖。其中,Convst為啟動轉換信號;Addr為通道地址;byte信號用于控制數據并行輸出的模式,低電平為低8位數據,高電平為高8位數據;ADdata 連接到AD7667的數據輸出端;數據通過ADdata輸入到FPGA。

圖5的數據轉換過程:A/D轉換器的數據采集是從Convst信號下降沿開始,Convst下降沿啟動對n-1通道的采樣轉換, 進入轉換進程后,通道地址信號a和p根據幀計數切換到采集通道n, 在等待足夠的轉換時間t4后,AD7667在byte高電平的控制下從AD[7:0]輸出n-1通道高8位的轉換數據,高8位數據在寫時鐘Wrclk的控制下,以足夠的時間傳輸給緩存器,AD7667在byte低電平的控制下從AD[7:0]輸出n-1通道低8位的轉換數據,低8位數據在寫時鐘Wrclk的控制下,以足夠的時間傳輸給緩存器,并在傳輸的同時進入n通道的采集過程,此時n通道信號在經過了時間t3后,已經達到穩定的電平。

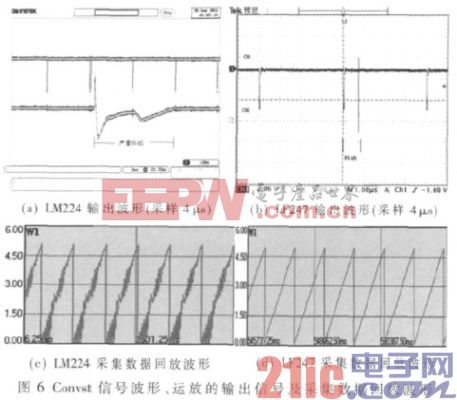

在采集的過程中測得的Convst信號波形與運放的輸出波形如圖6 (a)、(b)所示。

圖6 (a)、(b)中,CH1通道為Convst信號,頻率約為250 MHz(采樣周期4 μs),CH2通道為運放輸出信號。 圖6(c)、(d)分別為用LM224和LF247作為運放時采集數據的回放波形。從圖6 (a)、(b)可以看出,在開關切換的過程中,運算放大器輸出的信號存在劇烈抖動。圖6(a)中測得的是用LM224作為濾波跟隨器(SR為0.3 V/?滋s)的輸出信號,此濾波放大器的輸出抖動直到ADC采樣前還未穩定,導致采集到的數據波形出現嚴重失真,如圖6(c)所示;在圖6(b)中的豎線處,運放的輸出也存在一定的抖動,然而,由于濾波運放采用LF247(該運放的SR為16 V/?滋s),其輸出在ADC采樣前已經穩定到極高的精度,所以用該運放作為濾波跟隨器采集到的數據波形非常準確,如圖6(d)所示。

由此可以看出,與傳統的流水線順序相比較,由于硬件描述語言VHDL進程之間具有并發特性(進程(1)與進程(2)的并發性),這樣就必然節省了通道切換、采樣和保持的時間,同時結合硬件,選擇合適的運放,即可保證ADC轉換之前轉換通道信號的穩定,這就解決了通道串擾問題。

3.2 存儲邏輯設計

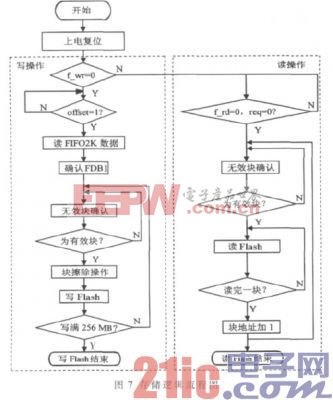

存儲邏輯主要包括對Flash的擦除、讀寫及識別無效塊。控制流程圖如圖7所示。

存儲器默認為讀狀態,上電復位時間設置為0.8 s,復位完成則判斷是否處于寫狀態,若是,則記錄采編器傳輸的數據,若否,則在讀請求信號有效時(低電平有效),送出Flash芯片內所存數據,送完256 MB自動停止。若中間讀請求信號無效,存儲器停止送數,維持當前狀態,并等待請求信號再次有效。

當存儲器處于寫狀態時,A、B片同時完成數據的記錄;當處于讀狀態時,在各自讀請求信號有效時,分時復用采編器數據總線,先后將兩套存儲器數據上傳。1#存儲器為默認優先上傳存儲器,通過設置采編器通道切換信號為有電流狀態,可選擇2#存儲器上傳數據。

備用讀數狀態下,分別讀取兩套存儲器。

評論