基于FPGA的實驗室可重構信號源的設計

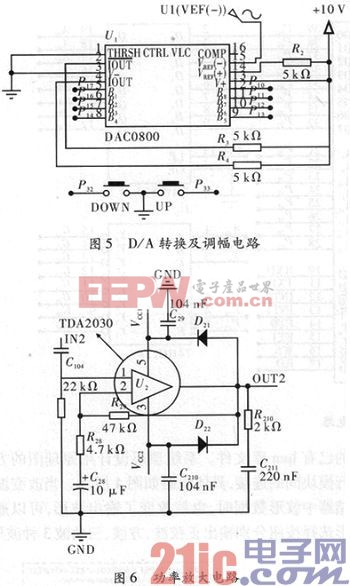

3.3 D/A轉換及調幅電路

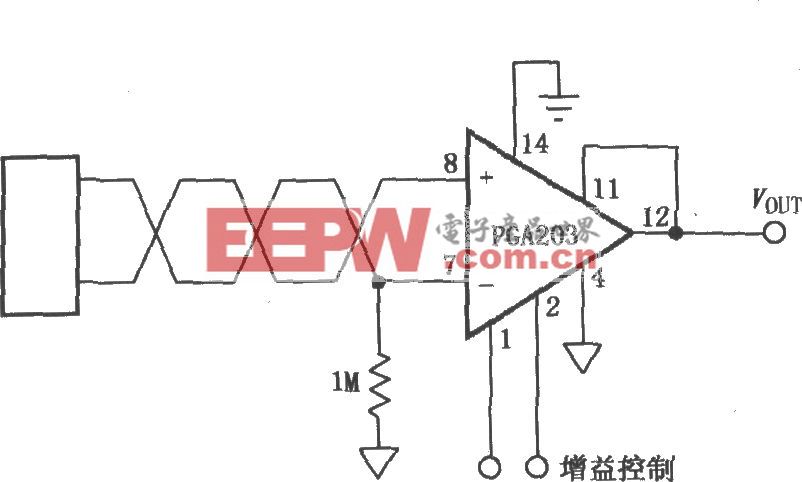

如圖5所示,將波形存儲ROM的輸出通過D/A轉換電路轉換為模擬信號,通過算法實現幅度控制并設置獨立按鍵執行微調,再通過濾波電路濾波,即可得到所需的波形。本文引用地址:http://www.104case.com/article/189605.htm

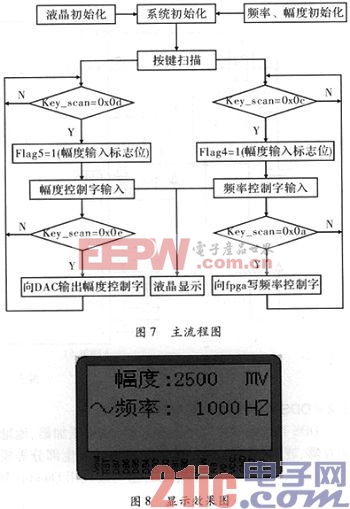

3.4 功率放大模塊

由于輸出信號的功率較小,輸出有負載時,會有較大失真,帶負載能力差,要考慮到功率放大,對輸出的信號進行放大。設計中功率放大采用功率放大芯片TDA2030A實現,TDA2030A是意法半導體公司生產的單聲道功放IC,該IC體積小巧、輸出功率大、靜態電流小、動態電流大、負載能力強,既可帶動4~16 Ω的負載,某些場合又可帶動2 Ω甚至1.6 Ω的低阻負載,且性價比高,具體電路如圖6所示。

3.2 DDS的FPGA實現電路設計

DDS系統包括相位增量寄存器、相位累加器、地址寄存器、波形存儲器、時鐘倍頻器及地址發生部分等模塊,內部所有模塊用Verilog語言編寫或調用QuartusⅡ中的已有lpm庫文件。系統頂層設計用原理圖的方式進行模塊間的連接,具體電路如圖4所示。當改變波形存儲器中波形數據時,也就改變了輸出波形,可以通過波形選擇按鈕分別輸出正弦波、方波、三角波3種波形。

3.3 D/A轉換及調幅電路

如圖5所示,將波形存儲ROM的輸出通過D/A轉換電路轉換為模擬信號,通過算法實現幅度控制并設置獨立按鍵執行微調,再通過濾波電路濾波,即可得到所需的波形。

3.4 功率放大模塊

由于輸出信號的功率較小,輸出有負載時,會有較大失真,帶負載能力差,要考慮到功率放大,對輸出的信號進行放大。設計中功率放大采用功率放大芯片TDA2030A實現,TDA2030A是意法半導體公司生產的單聲道功放IC,該IC體積小巧、輸出功率大、靜態電流小、動態電流大、負載能力強,既可帶動4~16 Ω的負載,某些場合又可帶動2 Ω甚至1.6 Ω的低阻負載,且性價比高,具體電路如圖6所示。

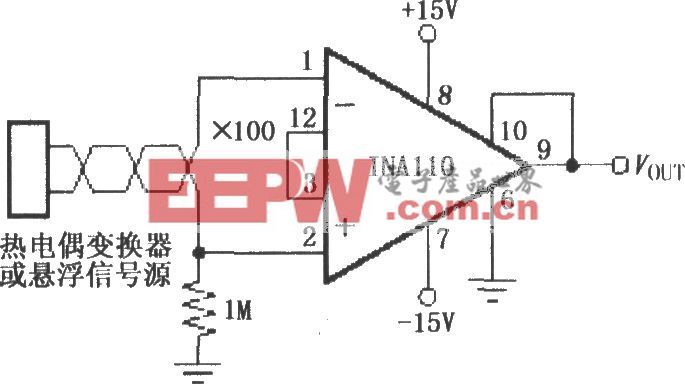

4 軟件設計

軟件設計采用C語言編寫。軟件主要由主程序、液晶子程序和按鍵子程序等組成。軟件主流程如圖7所示。系統加電后,主程序的功能主要是完成系統初始化,包括液晶、頻率幅度等參數的初始化,更新顯示數字,循環掃描按鍵,根據按鍵輸入分別進行頻率幅度的設定,通過幅度控制字的設定向DAC輸出幅度控制字,通過頻率控制字的輸入向FPGA寫頻率控制字,從而達到改變輸出波形頻率和幅值的目的,并在液晶顯示器上顯示出來。顯示效果如圖8所示。

5 結束語

系統采用FPGA實現DDS電路,以AT89C51為主控制器,實現了輸出頻率范圍為1 Hz~10 MHz的正弦波、方波、三角波的信號發生器,并且幅值和頻率均可調節,其最小步進頻率可達1 Hz。測試結果表明,該設計具有頻帶寬、精度高、性能穩定、成本低和操作界面友好等特點。用這種方法設計的波形發生器只要改變FPGA中ROM的數據,DDS就可以產生任意波形,提高了設計的靈活性,降低了電路的復雜度,減少了電路設計時間和可能發生的錯誤,具有較高的性價比。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

51單片機相關文章:51單片機教程

負離子發生器相關文章:負離子發生器原理 離子色譜儀相關文章:離子色譜儀原理

評論