基于FPGA的實驗室可重構信號源的設計

摘要 介紹了以直接頻率合成技術DDS為基礎的信號發生器基本工作原理及設計過程,并以單片機和FPGA為核心實現了波形、頻率、幅值均可調節的信號發生器設計。經測試驗證,該信號發生器取得了理想的結果,達到了設計要求。

關鍵詞 單片機;FPGA;DDS;信號發生器

1 直接數字頻率合成技術

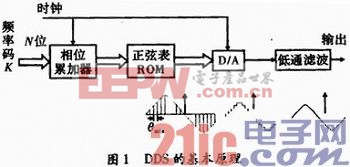

直接數字頻率合成技術(DDS)是近年來迅速發展的一種新型頻率合成方法,它將先進的數字處理理論與方法引入信號合成領域,通過控制相位變化的速度來直接產生各種不同頻率的信號。DDS的基本原理如圖1所示,把一個單位振幅的正弦函數的相位在2π弧度內分成2N個點,求出相應各點的正弦函數值,并用D位二進制數表示,寫入ROM中構成一個所謂的正弦表。在高速穩定的參考時鐘控制下依次讀出每個相位對應的正弦函數值,即得到采樣的正弦離散信號,經D/A轉換得到需要的模擬信號,改變輸入時鐘頻率即可控制輸出信號的頻率。

根據DDS的原理分析可知,DDS輸出波形頻率為fo=Kfc/2N。最低輸出頻率(K=1)fmin=fc/2N,最高輸出頻率為fmax=fc/4,其中,fc為累加時鐘頻率;K為頻率控制字;N為累加器位數。

2 系統整體方案設計

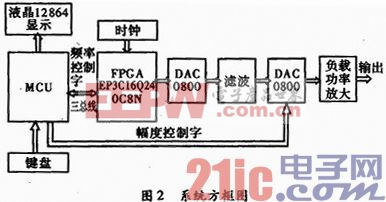

系統設計主要由主控制器模塊、FPGA模塊、D/A轉換模塊、濾波模塊、調幅模塊、按鍵輸入模塊、功率放大模塊及液晶顯示模塊構成。系統框圖如圖2所示。采用STC89C51單片機作為系統的主控制器;FPGA模塊實現波形數據的存儲與輸出;D/A轉換模塊將波形數據轉換為模擬量。液晶顯示器用于顯示波形、幅度、頻率等。

3 系統主要硬件電路設計

3.1 主控制器電路設計

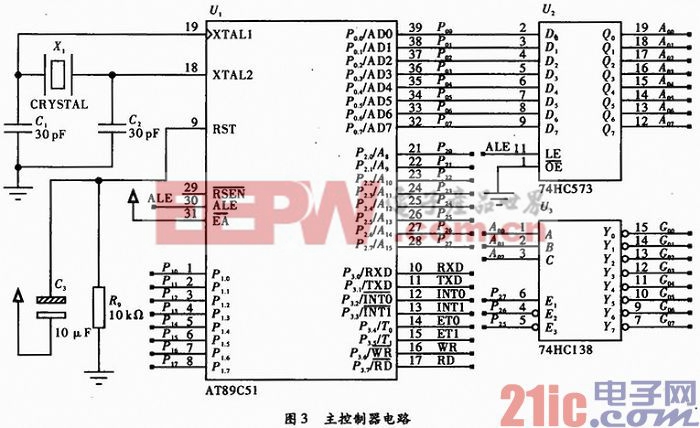

主控制器采用AT89C51單片機,系統采用總線技術,這樣僅占用了單片機的少量接口和IO資源就可以組建起整個系統,使得硬件和軟件設計更方便,也利于擴展,具體電路如圖3所示。

3.2 DDS的FPGA實現電路設計

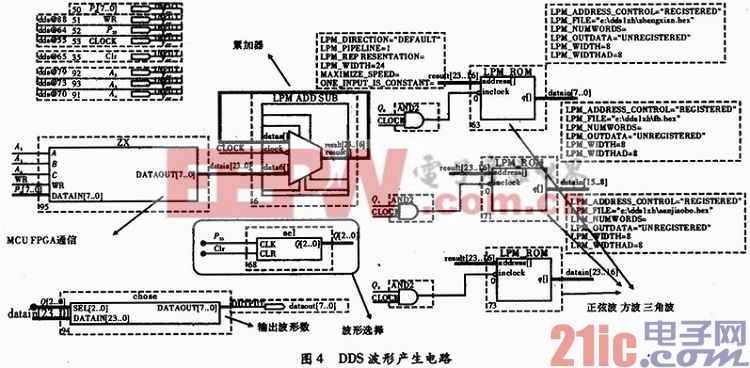

DDS系統包括相位增量寄存器、相位累加器、地址寄存器、波形存儲器、時鐘倍頻器及地址發生部分等模塊,內部所有模塊用Verilog語言編寫或調用QuartusⅡ中的已有lpm庫文件。系統頂層設計用原理圖的方式進行模塊間的連接,具體電路如圖4所示。當改變波形存儲器中波形數據時,也就改變了輸出波形,可以通過波形選擇按鈕分別輸出正弦波、方波、三角波3種波形。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

51單片機相關文章:51單片機教程

負離子發生器相關文章:負離子發生器原理 離子色譜儀相關文章:離子色譜儀原理

評論