基于FPGA的交通路口車流量檢測方法研究

2 基于FPGA的硬件仿真

FPGA即現場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。FPGA的使用非常靈活,同一片FPGA通過不同的編程數據可以產生不同的電路功能。FPGA在通信、數據處理、網絡、儀器、工業控制、軍事和航空航天等眾多領域得到了廣泛的應用。

文中通過使用matlab對上述算法進行仿真,我們可以得到視頻圖像每一幀的像素信息,并將該信息作為一個數據矩陣儲存到后綴名為dat的二進制數據文件中,作為FPGA硬件仿真的輸入激勵,即像素點檢測的輸入部分。

基于FPGA平臺來完成實時算法的硬件實現,文中根據算法復雜度及資源使用情況,選取Xilinx公司的SpartanIIIXC3S50芯片完成實現。

XC3S50是Xilinx公司推出的SpartanIII系列中資源可用量較少的一款芯片,它包含768個slices、4塊18x18乘法器、4塊獨立RAM(每塊RAM容量為18K)。經過綜合計算以及篩選,在節約成本的基礎上,確定XC3S50為交通信號燈路口的車流量檢測算法的硬件實現平臺。

電路設計的開發環境采用ise12.4,并使用modelsim6.5se進行硬件電路仿真。本文引用地址:http://www.104case.com/article/189598.htm

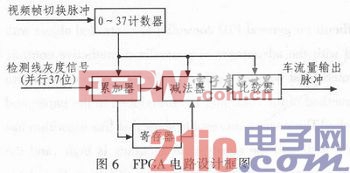

如圖6所示,視頻幀切換脈沖到來時啟動計數器進行時序控制計數,計數到37后保持,等待下一個脈沖的啟動,在計數過程中將數值輸出至其他電路。累加器接收到計數后,對每一幀更新的并行灰度信號進行逐位累加處理,當37位累加完畢,輸出累加結果至減法器。減法器在時序計數控制下將當前幀的累加值與寄存器存放的上一幀灰度累加值做差,將結果輸出至比較器。比較器將差值與門限值進行比較,如果超過門限,則輸出一個高脈沖,作為有車經過的標志。

仿真采用的系統時鐘為65.536 MHz,對應時鐘周期約為15.2 ns,如圖7所示,每一幀的處理時間僅需38*15.2 ns≈577 ns,可以滿足快速處理的需要。圖中output_signal為比較器輸出的結果,即為監測是否有車輛通過的標志,該結果與matlab算法仿真結果完全一致。該算法實現簡單,有很高的實時性和可操作性。

3 結束語

文中的算法是利用Matlab編程實現的,而硬件實現是在isel2.4+modelsim6.5se的環境下編譯完成的。通過對一段3分48秒的交通路口視頻進行驗證,準確率在97%以上。文中與其他實現車流量統計的算法相比較,優點在于完成該算法的硬件實現,且就算法本身而言,實現簡單,數據處理量小,處理速度快。但該算法自適應性較弱,容易受到外界干擾影響,需要進一步加強對檢測算法的優化和改進研究,以提高檢測算法的準確度和自適應性。

評論