FPGA設(shè)計小Tips:如何正確使用FPGA的時鐘資源

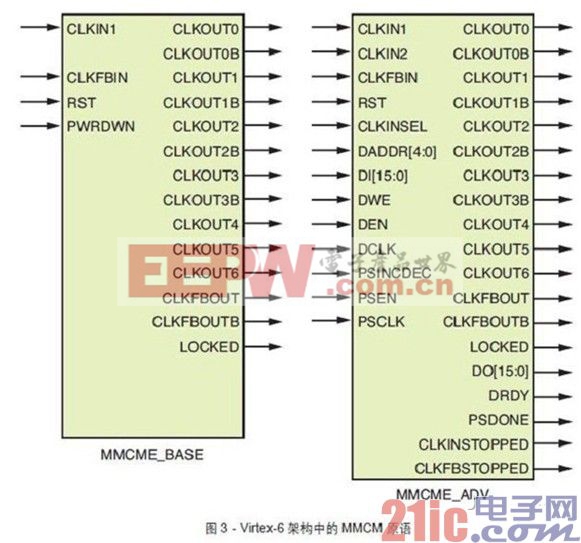

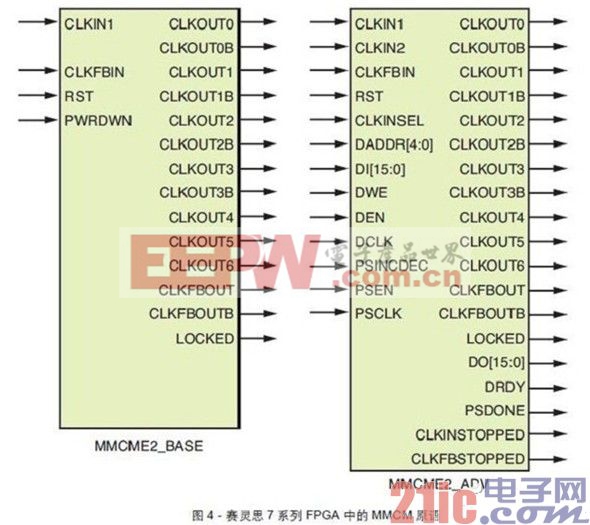

圖 3顯示了Virtex-6FPGA中的MMCM原語。各個端口的詳細介紹請參閱Virtex-6FPGA時鐘資源用戶指南(UG362,2.1版本)。圖 4顯示了賽靈思7系列FPGA中的MMCM原語,有關(guān)詳細介紹請參閱7系列FPGA時鐘資源用戶指南(UG472,1.5版本)。

鎖相環(huán)

設(shè)計人員使用鎖相環(huán)(PLL)主要用于頻率綜合。使用一個PLL可以從一個輸入時鐘信號生成多個時鐘信號。結(jié)合DCM使用,還可以用作抖動濾波器。Spartan-6、Virtex-5和7系列FPGA中都提供有PLL。Spartan-6和 Virtex-5中均有專門的“DCM到PLL”和“PLL到DCM”走線。Spartan-6和Virtex-5中的PLL輸出是非擴頻的。對這兩種器件而言,如果設(shè)計使用多個不同時鐘,都可以用PLL替代DCM。PLL時鐘輸出具有寬范的配置范圍,而DCM的輸出是預(yù)定的,不可配置。PLL和DCM的選擇還是取決于設(shè)計的要求。不過如果相移是必需的,就應(yīng)該明確地選擇DCM。

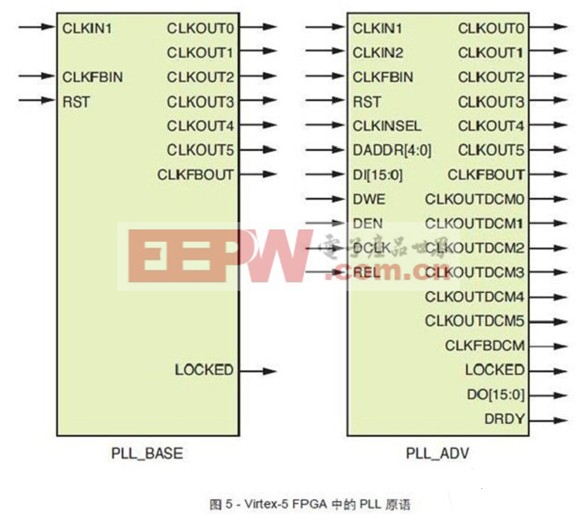

同時,7系列器件中的PLL所實現(xiàn)的功能沒有 MMCM所實現(xiàn)的多。因此雖然MMCM是建立在PLL架構(gòu)之上,但7系列器件中也有獨立的PLL。圖5顯示了Virtex-5FPGA中的PLL原語。各個端口的詳細介紹請參閱Virtex-5用戶指南(UG190,5.4版本)。

設(shè)計移植

掌握四種主要的時鐘資源之間的差異及其在不同器件系列中的可用性非常重要。同時,在不同的系列中,相似的資源(比如DCM)可能在功能上并不完全相同。例如,Spartan-6FPGA中的DCM支持?jǐn)U頻時鐘,但Virtex-5和Virtex-5器件中的DCM就不支持。

在規(guī)劃未來設(shè)計向更高端系列移植時,除了確保功能,為給定設(shè)計選擇正確的時鐘資源也很重要。如表1所示,Virtex-6和7系列中的MMCM能夠與之前系列中的DCM向后兼容。但需要判斷在多大程度上支持向后兼容性,因為所有這些時鐘資源都具有多功能性,提供與時鐘相關(guān)的多種不同功能。在制定產(chǎn)品長期發(fā)展規(guī)劃時,必須對兼容性了如指掌。

分頻器相關(guān)文章:分頻器原理

評論