FPGA設計小Tips:如何正確使用FPGA的時鐘資源

相位匹配時鐘分頻器

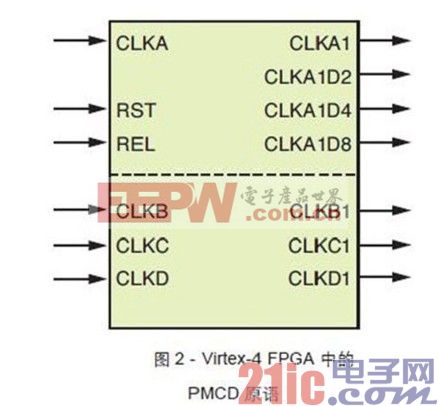

設計人員可使用相位匹配時鐘分頻器(PMCD)來生成相位匹配的分頻輸入時鐘信號。這與分頻時鐘的DCM頻率綜合相似。PMCD還能生成設計中相位匹配但有延遲的時鐘信號。在后一種情況下,PCMD能夠在輸入時鐘信號和其它PMCD輸入時鐘信號之間保持邊緣對齊、相位關系和歪斜。與DCM不同的是,在分頻器的值可配置的情況下,賽靈思器件中現有的PMCD生成的時鐘信號僅按2、4和8分頻。這意味著PMCD生成的時鐘信號的頻率是輸入時鐘信號的1/2、1/4和1/8。在如Virtex-4FPGA這樣的賽靈思器件中,PMCD緊鄰 DCM并與其位于同一列上。每一列有兩個PMCD-DCM對。因此DCM的輸出可以驅動PMCD的輸入。

由于DCM還負責處理去歪斜,因此只要不需要去歪斜時鐘,設計人員就可以使用不帶DCM的PMCD。通過專用引腳,還可以把一列中的兩個PMCD連接起來。圖2是 Virtex-4器件中的PMCD原語。詳細內容請參閱Virtex-4FPGA用戶指南(UG070,2.6版本)。

混合模式時鐘管理器

另一種類型的時鐘資源——混合模式時鐘管理器(MMCM),用于在與給定輸入時鐘有設定的相位和頻率關系的情況下,生成不同的時鐘信號。不過與DCM不同是,MMCM使用PLL來完成這一工作。Virtex-6FPGA中的時鐘管理模塊(CMT)有兩個MMCM,而Virtex-7中的CMT有一個 MMCM和一個PLL。Virtex-6器件中的MMCM沒有擴頻功能,因此輸入時鐘信號上的擴頻不會被濾波,將直接被傳送給MMCM輸出時鐘。但 Virtex-7FPGA的MMCM卻有擴頻功能。

Virtex-6FPGA中的MMCM要求插入一個校準電路,以便在用戶復位或用戶斷電后確保MMCM正確運行。賽靈思ISE設計套件11.5版本及更高版本能夠在設計的MAP階段自動插入必要的校準電路。若使用賽靈思ISE 的更早版本,則需要使用賽靈思技術支持部提供的設計文件手動插入校準電路。最后需要注意的是,在本移植該設計,以便用ISE11.5版本或更高版本實現時,必須手動移除校準電路,或通過適當設置每個MMCM上的綜合屬性,禁用自動插入功能。詳細介紹請參閱賽靈思答復記錄AR#33849。

對7系列器件中的MMCM就不存在這樣的問題,因為這些FPGA只得到ISE13.1版本和更高版本以及新型Vivado設計套件的支持。Virtex-6系列中提供的MMCM間專用走線可便于用戶將全局時鐘資源用于設計的其余部分。

分頻器相關文章:分頻器原理

評論