FPGA最小系統電路分析之FPGA管腳設計

FPGA的管腳主要包括:用戶I/O(User I/O)、配置管腳、電源、時鐘及特殊應用管腳等。其中有些管腳可有多種用途,所以在設計FPGA電路之前,需要認真的閱讀相應FPGA的芯片手冊。

下面以Altera公司的Cyclone系列FPGA為例,介紹FPGA的各種功能管腳。

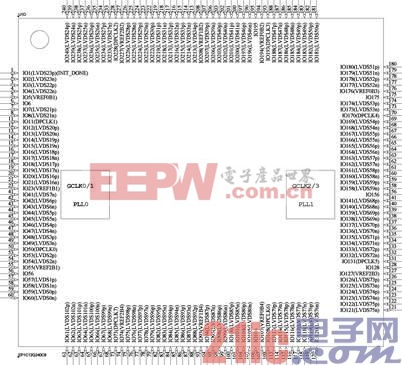

(1)用戶I/O。

I/Onum(LVDSnumn):可用作輸入或輸出,或者雙向口,同時可作為LVDS差分對的負端。其中num表示管腳序號。

一般在繪制FPGA原理圖時,將同一種功能和用途的管腳放在一個框圖中,如圖2.3所示是用戶I/O的原理圖。

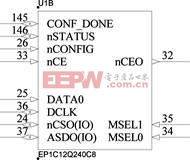

(2)配置管腳。

MSEL[1..0]:用于選擇配置模式。FPGA有多種配置模式,比如主動、被動、快速、正常、串行、并行等,可以此管腳進行選擇。

DATA0:FPGA串行數據輸入,連接至配置器件的串行數據輸出管腳。

DCLK:FPGA串行時鐘輸出,為配置器件提供串行時鐘。

nCSO(I/O):FPGA片選信號輸出,連接至配置器件的nCS管腳。

ASDO(I/O):FPGA串行數據輸出,連接至配置器件的ASDI管腳。

nCEO:下載鏈器件使能輸出。在一條下載鏈(Chain)中,當第一個器件配置完成后,此信號將使能下一個器件開始進行配置。下載鏈的最后一個器件的nCEO應懸空。

圖2.3 FPGA用戶I/O原理圖

nCE:下載鏈器件使能輸入,連接至上一個器件的nCEO。下載鏈第一個器件的nCE接地。

nCONFIG:用戶模式配置起始信號。

nSTATUS:配置狀態信號。

CONF_DONE:配置結束信號。

如圖2.4所示是FPGA配置管腳原理圖。

圖2.4 FPGA配置管腳原理圖

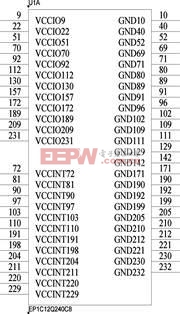

(3)電源管腳。

VCCINT:內核電壓。通常與FPGA芯片所采用的工藝有關,例如130nm工藝為1.5V,90nm工藝為1.2V。

VCCIO:端口電壓。一般為3.3V,還可以支持選擇多種電壓,如5V、1.8V、1.5V等。

VREF:參考電壓。

GND:信號地。

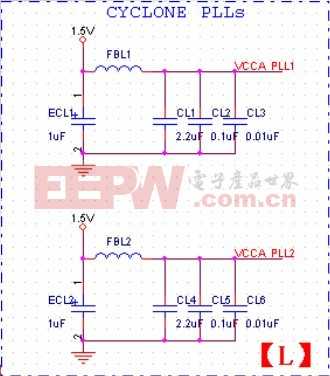

(4)時鐘管腳。

VCC_PLL:鎖相環管腳電壓,直接連VCCIO。

VCCA_PLL:鎖相環模擬電壓,一般通過濾波器接到VCCINT上。

GNDA_PLL:鎖相環模擬地。

GNDD_PLL:鎖相環數字地。

CLKnum(LVDSCLKnump):鎖相環時鐘輸入。支持LVDS時鐘輸入,p接正端,num表示PLL序號。

CLKnum(LVDSCLKnumn):鎖相環時鐘輸入。支持LVDS時鐘輸入,n接負端,num表示PLL序號。

PLLnum_OUTp(I/O):鎖相環時鐘輸出。支持LVDS時鐘輸入,p接正端,num表示PLL序號。

PLLnum_OUTn(I/O):鎖相環時鐘輸出。支持LVDS時鐘輸入,n接負端,num表示PLL序號。

如圖2.6所示是FPGA時鐘管腳原理圖。

圖2.5 FPGA電源管腳原理圖 圖2.6 FPGA時鐘管腳原理圖

另外,FPGA的管腳中,有一些是全局時鐘,這些管腳在FPGA中已經做好了時鐘樹。使用這些管腳作為關鍵時鐘或信號的布線可以獲得最佳性能。

(5)特殊管腳。

VCCPD:用于選擇驅動電壓。

VCCSEL:用于控制配置管腳和鎖相環相關的輸入緩沖電壓。

PORSEL:上電復位選項。

NIOPULLUP:用于控制配置時所使用的用戶I/O的內部上拉電阻是否工作。

TEMPDIODEn/p:用于關聯溫度敏感二極管。

fpga相關文章:fpga是什么

上拉電阻相關文章:上拉電阻原理 鎖相環相關文章:鎖相環原理

評論